# Министерство образования Российской Федерации Государственный университет аэрокосмического приборостроения кафедра Радиотехнические системы

# Лабораторная плата UP1 фирмы Altera

Пособие подготовлено на кафедре Радиотехнические системы Санкт-Петербургского Государственного университета аэрокосмического приборостроения. Пособие подготовлено на основе описания **University Program Design Labaratory Package** (December 1999, ver. 1.02) фирмы **Altera**.

- Редактор: с. н. с. кафедры РТС, к.т.н. Р.А. Мяльк.

- Компьютерная верстка: с. н. с. кафедры РТС, к.т.н. Р.А. Мяльк.

- Перевод: студент гр. 2901 С.С. Поддубный.

- Приведенное в приложении 3 текстовое описание на языке VHDL подготовлено студентом гр. 2702 Н. А. Даниловым.

#### Содержание

| 1. Общая характеристика платы UP1                              | 4  |

|----------------------------------------------------------------|----|

| 2. Основные электронные компоненты платы UP1                   | 5  |

| 2.1. Компоненты общего назначения                              | 5  |

| 2.1.1. Разъем подключения внешнего источника питания           | 5  |

| 2.1.2. Встроенный стабилизатор напряжения питания              | 6  |

| 2.1.3. Тактовый генератор                                      | 6  |

| 2.1.4. Входной разъём интерфейса JTAG                          | 6  |

| 2.1.5. Установочные переключатели режимов конфигурации         |    |

| 2.2. Компоненты, относящиеся к микросхеме семейства МАХ7000    | 8  |

| 2.2.1. Дублирующие разъемы микросхемы ЕРМ7128                  | 8  |

| 2.2.2. Кнопочные переключатели МАХ_РВ1 и МАХ_РВ2               | 9  |

| 2.2.3. Задающие переключатели MAX_SW1 и MAX_SW2                | 9  |

| 2.2.4. Контрольные гнезда и светодиоды                         | 9  |

| 2.2.5. Знакосинтезирующий индикатор микросхемы EPM7128S        | 9  |

| 2.2.6. Разъём расширения микросхемы МАХ7000                    | 10 |

| 2.3. Компоненты, относящиеся к микросхеме семейства FLEX10K    | 12 |

| 2.3.1. Кнопочные переключатели микросхемы EPF10K20             | 12 |

| 2.3.2. Задающие переключатели микросхемы EPF10K20              | 12 |

| 2.3.3. Знакосинтезирующий индикатор микросхемы EPF10K20        | 13 |

| 2.3.4. Выходной адаптер и разъем VGA-монитора                  |    |

| 2.3.5. Входной разъем устройства "мышь"                        |    |

| 2.3.6. Разъёмы расширения микросхемы EPF10K20                  | 14 |

| 3. Приложение 1. Программирование и конфигурирование микросхем |    |

| 4. Приложение 3. Характеристика последовательного интерфейса   |    |

| 5. Приложение 2. Характеристика монитора VGA                   | 24 |

| б. Приложение 3. Пример формирования сигналов монитора VGA     | 26 |

| 7. Глоссарий                                                   | 29 |

# Список иллюстраций

| Рис 1. Схема расположения элементов на плате UP1                   | 5    |

|--------------------------------------------------------------------|------|

| Рис 2. Переключатели выбора режимов конфигурирования               |      |

| Рис 3. Контрольные гнезда и светодиоды платы UP1                   |      |

| Рис 4. Обозначение сегментов знакосинтезирующих индикаторов        | 10   |

| Рис 5. Разъем расширения микросхемы EPM7128S на плате UP1          | 10   |

| Рис 6. Разъемы расширения микросхемы EPF10K20 на плате UP1         | . 14 |

| Рис 7. Установка режима программирования микросхемы EPM7128S       | 18   |

| Рис 8. Установка режима конфигурирования микросхемы EPF10K20       | 19   |

| Рис 9. Установка режима совместного конфигурирования микросхем     |      |

| Рис 10. Установка режима конфигурирования платы UP1 в JTAG-цепочке | 21   |

| Рис 11. Установка режима конфигурирования оконечной платы UP1      | 22   |

| Рис 12. Поле отображения монитора VGA                              | 24   |

| Рис 13. Временные диаграммы строчной синхронизации VGA             |      |

| Рис 14. Временные диаграммы кадровой синхронизации VGA             | 24   |

| Converse mass mass many                                            |      |

| Список таблиц                                                      | -    |

| Таблица 1. Контакты разъема JTAG_IN                                |      |

| Таблица 2. Установка режимов конфигурирования                      | /    |

| Таблица 3. Дублирующие разъемы микросхемы ЕРМ7128                  |      |

| Таблица 4. Семисегментные индикаторы микросхемы EPM7128S           |      |

| Таблица 5. Разъем расширения микросхемы ЕРМ7128S                   |      |

| Таблица 6. Задающий DIP-переключатель FLEX_SW1                     |      |

| Таблица 7. Семисегментные индикаторы микросхемы EPF10K20           |      |

| Таблица 8. Контакты разъема VGA                                    |      |

| Таблица 9. Контакты разъема PS/2                                   |      |

| Таблица 10. Контакты разъема FLEX_EXPAN_A                          |      |

| Таблица 11. Контакты разъема FLEX_EXPAN_B                          |      |

| Таблица 12. Контакты разъема FLEX_EXPAN_C                          |      |

| Таблица 15. Формат пакета данных последовательного интерфейса      |      |

| Таблица 13. Параметры строчной синхронизации VGA                   |      |

| Таблица 14. Параметры кадровой синхронизации VGA                   | 25   |

# 1. Общая характеристика платы UP1

Лабораторная плата  $\mathbf{UP1}^1$  фирмы Altera предназначена для отработки вопросов практической реализации учебных проектов цифровых устройств на ПЛИС Altera.

На плате расположены две микросхемы: одна семейства **FLEX10K** (тип **EPF10K20**), вторая – семейства **MAX7000** (тип **EPM7128S**). Каждой микросхеме отведены аппаратные ресурсы, включающие элементы конфигурирования, элементы индикации, нефиксируемые кнопочные выключатели, DIPпереключатели, задающие на выводах микросхем логические уровни "0" и "1", разъемы расширения для подключения внешних устройств и ряд других элементов.

Плата имеет выходной разъем для подключения стандартного монитора **VGA** и входной разъем **PS/2 Mini-Din** для подключения последовательных устройств ("мышь" и клавиатура). Монитор **VGA** и последовательне устройства подключаются только к микросхеме семейства **FLEX10K**.

Загрузка конфигурирующих данных в микросхемы осуществляется через установленный на плате входной разъем интерфейса **JTAG**. Наличие второго (выходного) разъема **JTAG** обеспечивает конфигурирование нескольких плат **UP1**, объединенных в JTAG-цепочку.

Кроме того, для хранения и загрузки конфигурации микросхемы **EPF10K20** может быть использовано конфигурационное ПЗУ типа **EPC1**, для которого предусмотрен соответствующий установочный разъем.

Загрузка конфигурации из персонального компьютера осуществляется с помощью устройства **ByteBlaster**. Устройство **ByteBlaster** подключается к параллельному порту персонального компьютера и соединяется кабелем со входным разъемом **JTAG** платы **UP1**.

Плата **UP1** имеет встроенный 5-ти вольтовый стабилизатор напряжения питания и работает от внешнего нестабилизированного источника питания постоянного тока.

<sup>&</sup>lt;sup>1</sup> Лабораторная плата UP1 выпускается фирмой Altera в рамках так называемой университетской программы Universyty Program – UP (прим. ред.).

ГУАП кафедра "Радиотехнические системы"

# 2. Основные электронные компоненты платы UP1

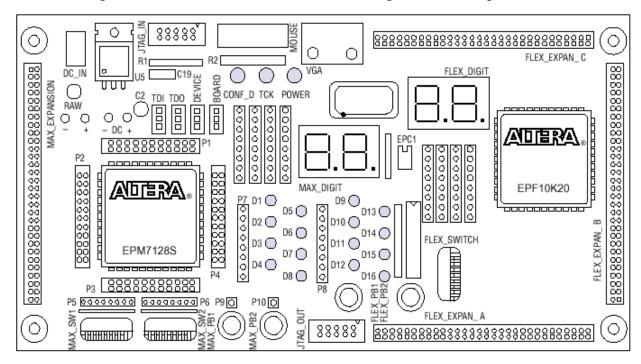

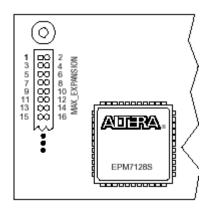

В этом разделе описаны основные электронные компоненты платы **UP1**. Схема расположения элементов на плате приведена на рис. 1.

Рис 1. Схема расположения элементов на плате UP1

#### 2.1. Компоненты общего назначения

#### 2.1.1. Разъем подключения внешнего источника питания

Для подключения внешнего источника питания служит коаксиальный разъем, обозначенный надписью **DC\_IN**.

Разъем имеет типоразмеры 2,5 мм × 5,5 мм.

Внутренний контакт разъема – положительный "+".

Внешний контакт разъема – общий провод "-".

Требования к внешнему (нестабилизированному) источнику питания:

- Диапазон подводимого постоянного напряжения от 7 до 9 В,

- Ток нагрузки не менее 350 мА.

На плате имеются контрольные контактные площадки подводимого внешнего питания, обозначенные надписью  $\mathbf{RAW}$  ("+" – положительный, "-" – общий провод).

#### 2.1.2. Встроенный стабилизатор напряжения питания

Плата **UP1** имеет встроенный интегральный стабилизатор напряжения питания (тип **LM340T**) с выходным напряжением 5 В.

Наличие напряжения питания платы **UP1** индицируется зеленым светодиодом.

На плате имеются контрольные контактные площадки стабилизированного питания, обозначенные надписью  $\mathbf{DC}$  ("+" — положительный, "-" — общий провод).

#### 2.1.3. Тактовый генератор

Плата **UP1** содержит кварцевый тактовый генератор с частотой 25.175 МГц. Выход генератора подключен к глобальным тактовым входам микросхем **EPM7128S** (вывод 83) и **EPF10K20** (вывод 91).

#### 2.1.4. Входной разъём интерфейса JTAG

Разъем JTAG\_IN служит для подключения к плате UP1 кабеля загрузочного устройства ByteBlaster. Через разъем JTAG\_IN на ByteBlaster подается питание от платы UP1.

| Контакт | Сигнал JTAG     | Назначение           |

|---------|-----------------|----------------------|

| 1       | TCK             | Тактовые импульсы    |

| 2       | GND             | Земля                |

| 3       | TDO             | Выход данных         |

| 4       | VCC             | + Напряжения питания |

| 5       | TMS             | Управление конечным  |

| 3       | 1 WIS           | автоматом JTAG       |

| 6       | Не задействован | -                    |

| 7       | Не задействован | -                    |

| 8       | Не задействован | -                    |

| 9       | TDI             | Вход данных          |

| 10      | GND             | Земля                |

Таблица 1. Контакты разъема JTAG IN

# 2.1.5. Установочные переключатели режимов конфигурации

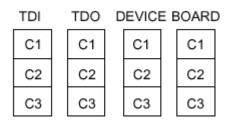

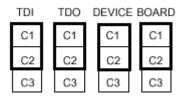

Для установки режимов конфигурирования плата **UP1** содержит четыре 3-х контактных переключателя, выполненных в виде штыревых контактов, замыкаемых перемычками (джамперами).

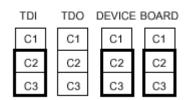

Переключатели на плате имеют следующие обозначения (см. рис. 2):

- **TDI** вход данных,

- **TDO** выход данных,

- **DEVICE** микросхема,

- **BOARD** плата.

Надписями **C1**, **C2**, **C3** на рис. 2 обозначены штыревые контакты переключателей.

Возможны различные режимы конфигурации (см. приложение 1): программирование микросхемы **EPM7128S**, конфигурирование микросхемы, **EPF10K20**, совместное конфигурирование обеих микросхем, конфигурирование нескольких плат **UP1**, соединенных через входные-выходные разъемы **JTAG\_IN** и **JTAG\_OUT**.

Режимы конфигурирования и соответствующие им положения перемычек приведены в таблице 2.

Рис 2. Переключатели выбора режимов конфигурирования

| Режим                                           | TDI   | TDO   | DEVICE | BOARD |

|-------------------------------------------------|-------|-------|--------|-------|

| Программирование микросхемы                     | C1&C2 | C1&C2 | C1&C2  | C1&C2 |

| Конфигурирование микросхемы                     | C2&C3 | C2&C3 | C1&C2  | C1&C2 |

| Совместное конфигурирование обеих микросхем (1) | C2&C3 | C1&C2 | C2&C3  | C1&C2 |

| Объединение нескольких плат UP1 (2)             | C2&C3 | OPEN  | C2&C3  | C2&C3 |

Таблица 2. Установка режимов конфигурирования

При совместном конфигурировании устройств в JTAG-цепочке действуют следующие правила:

- первым устройством в JTAG-цепочке должна быть микросхема **EPF10K20**, вторым микросхема **EPM7128S**:

- Последняя плата в JTAG-цепочке не должна устанавливаться в режим объединения плат.

Для контроля процесса конфигурирования служат два светодиода:

- Мигание зеленого светодиода ТСК индицирует передачу данных,

- Зажигание светодиода **CONF\_D** сигнализирует об успешном окончании передачи.

$<sup>^2</sup>$  Для микросхем семейств MAX фирмой Altera применяется термин "**программирование**", тогда как для микросхем семейств FLEX и некоторых микросхем семейства MAX применяется термин "**конфигурирование**" (прим. ред.).

ГУАП кафедра "Радиотехнические системы"

#### 2.2. Компоненты, относящиеся к микросхеме семейства МАХ7000

Микросхеме EPM7128S доступны следующие ресурсы:

- Установочный разъем ("кроватка") для корпуса **PLCC** с 84 контактами.

- Разъем JTAG подключения загрузочного кабеля ByteBlaster.

- Два оперативных нефиксируемых кнопочных переключателя.

- Два 8-разрядных задающих DIP-переключателя уровней "0" и "1".

- Контрольные контактные гнезда сигнальной шины.

- 16 светодиодов, сигнальной шины.

- Знакосинтезирующий индикатор, включающий два семисегментных знакоместа.

- Выход тактового генератора (25.175 МГЦ).

- Разъем расширения с 42 контактами ввода/вывода и контакты глобальных синхросигналов CLR, OE1, и OE2/GCLK2.

#### 2.2.1. Дублирующие разъемы микросхемы ЕРМ7128

Дублирующие разъемы микросхемы **EPM7128**. - расположены по периметру микросхемы и позволяют подключать внешние сигналы к контактам микросхемы.

По 21 контакту на каждой стороне 84-контактного корпуса **PLCC** соединяются с соответствующим 22-контактным разъемом. Номера контактов микросхемы EPM7128S обозначены на самой плате **UP1**. Символом "X" обозначены контакты без номера. Подключение контактов дублирующих разъемов P1, P2, P3, и P4 показано в таблице 3. Питание, земля и контакты JTAG через эти разъемы не подключаются.

Таблица 3. Дублирующие разъемы микросхемы ЕРМ7128

|         | P1         | I       | 22         | ]       | P3         | ]       | P4         |

|---------|------------|---------|------------|---------|------------|---------|------------|

| Внешний | Внутренний | Внешний | Внутренний | Внешний | Внутренний | Внешний | Внутренний |

| 75      | 76         | 12      | 13         | 33      | 34         | 54      | 55         |

| 77      | 78         | 14      | 15         | 35      | 36         | 56      | 57         |

| 79      | 80         | 16      | 17         | 37      | 38         | 58      | 59         |

| 81      | 82         | 18      | 19         | 39      | 40         | 60      | 61         |

| 83      | 84         | 20      | 21         | 41      | 42         | 62      | 63         |

| 1       | 2          | 22      | 23         | 43      | 44         | 64      | 65         |

| 3       | 4          | 24      | 25         | 45      | 46         | 66      | 67         |

| 5       | 6          | 26      | 27         | 47      | 48         | 68      | 69         |

| 7       | 8          | 28      | 29         | 49      | 50         | 70      | 71         |

| 9       | 10         | 30      | 31         | 51      | 52         | 72      | 73         |

| 11      | X          | 32      | X          | 53      | X          | 74      | X          |

#### 2.2.2. Кнопочные переключатели МАХ РВ1 и МАХ РВ2

Два кнопочных нефиксируемых переключателя **MAX\_PB1** и **MAX\_PB2** соединены с контактами на плате. При нажатии переключатели замыкают указанные контакты на общий провод через резистор 10 кОм. Переключатели могут быть подключены к контактам микросхемы **EPM7128S** соединительными проводами.

#### 2.2.3. Задающие переключатели MAX\_SW1 и MAX\_SW2

Задающие DIP-переключатели MAX\_SW1 и MAX\_SW2 содержит по восемь переключателей, которые позволяют задавать сигналы логического уровня на связанных с ними контактах. Разомкнутое состояние выключателя соответствует логической "1", замкнутое — логическому "0". Переключатели могут быть подключены к контактам микросхемы **EPM7128S** соединительными проводами.

#### 2.2.4. Контрольные гнезда и светодиоды

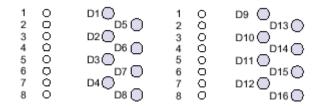

Плата **UP1** содержит 16 контрольных гнезд и 16 светодиодов (см. рис. 3.). Ток через светодиоды задается резисторами номиналом 330 Ом. Зажигание каждого светодиода осуществляется логическим "0". Светодиоды D1, D2, ..., D16 соединены соответственно с контрольными гнездами 1, 2, ..., 16.

Рис 3. Контрольные гнезда и светодиоды платы UP1

# 2.2.5. Знакосинтезирующий индикатор микросхемы EPM7128S

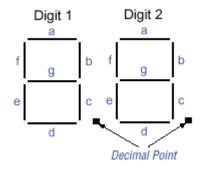

Знакосинтезирующий индикатор микросхемы **EPM7128S** обозначен надписью **MAX\_DIGIT.** Индикатор включает два знакоместа, выполненных на семисегментных индикаторах с общим катодом. Соответственно зажигание сегментов осуществляется логическим "0". Обозначение сегментов индикаторов приведено на рис. 4. Подключение сегментов к контактам микросхемы **EPM7128S** поясняется таблицей 4.

Рис 4. Обозначение сегментов знакосинтезирующих индикаторов Таблица 4. Семисегментные индикаторы микросхемы EPM7128S

| Сегмент       | Контакты микросхемы, подключенные к первому знакоместу | Контакты<br>микросхемы,<br>подключенные ко<br>второму знакоместу |

|---------------|--------------------------------------------------------|------------------------------------------------------------------|

| a             | 58                                                     | 69                                                               |

| b             | 60                                                     | 70                                                               |

| c             | 61                                                     | 73                                                               |

| d             | 63                                                     | 74                                                               |

| e             | 64                                                     | 76                                                               |

| f             | 65                                                     | 75                                                               |

| g             | 67                                                     | 77                                                               |

| Decimal point | 68                                                     | 79                                                               |

#### 2.2.6. Разъём расширения микросхемы МАХ7000

Разъём расширения **MAX\_EXPANSION** служит для подачи на микросхему **EPM7128S** сигналов ввода-вывода, глобальных сигналов, а также питания и земли.

Расположение разъема и нумерация его контактов показаны на рис. 5. Соответствие контактов разъема – контактам микросхемы **EPM7128S** дается таблицей 5.

Рис 5. Разъем расширения микросхемы EPM7128S на плате UP1

Таблица 5. Разъем расширения микросхемы EPM7128S

| Контакт разъема | Сигнал/контакт<br>микросхемы | Контакт разъема | Сигнал/контакт<br>микросхемы |

|-----------------|------------------------------|-----------------|------------------------------|

| 1               | RAW                          | 2               | GND                          |

| 3               | VCC                          | 4               | GND                          |

| 5               | VCC                          | 6               | GND                          |

| 7               | Не задействован              | 8               | Не задействован              |

| 9               | Не задействован              | 10              | Не задействован              |

| 11              | Не задействован              | 12              | GCLRn/1                      |

| 13              | OE/84                        | 14              | OE/GCLK2/2                   |

| 15              | 4                            | 16              | 5                            |

| 17              | 6                            | 18              | 8                            |

| 19              | 9                            | 20              | 10                           |

| 21              | 11                           | 22              | 12                           |

| 23              | 15                           | 24              | 16                           |

| 25              | 17                           | 26              | 18                           |

| 27              | 20                           | 28              | 21                           |

| 29              | 22                           | 30              | 25                           |

| 31              | 24                           | 32              | 27                           |

| 33              | 29                           | 34              | 28                           |

| 35              | 31                           | 36              | 30                           |

| 37              | 33                           | 38              | 34                           |

| 39              | 35                           | 40              | 36                           |

| 41              | 37                           | 42              | 40                           |

| 43              | 39                           | 44              | 41                           |

| 45              | 44                           | 46              | 46                           |

| 47              | 45                           | 48              | 48                           |

| 49              | 50                           | 50              | 49                           |

| 51              | 52                           | 52              | 51                           |

| 53              | 54                           | 54              | 55                           |

| 55              | 56                           | 56              | 57                           |

| 57              | VCC                          | 58              | GND                          |

| 59              | VCC                          | 60              | GND                          |

#### 2.3. Компоненты, относящиеся к микросхеме семейства FLEX10K

Плата **UP1** имеет следующие ресурсы для устройства EPF10K20. Выводы от устройства **EPF10K20** связаны с переключателем и светодиодами.

Микросхеме **EPF10K20** доступны следующие ресурсы:

- Разъем **JTAG** подключения загрузочного кабеля устройства **ByteBlaster**.

- Установочный разъем (кроватка) для конфигурационного ПЗУ **EPC1**.

- Выход тактового генератора (25.175 МГЦ)

- Два оперативных нефиксируемых кнопочных переключателя.

- Задающий 8-разрядный DIP-переключатель уровней "0" и "1".

- Контрольные контактные гнезда сигнальной шины.

- 16 светодиодов, сигнальной шины.

- Знакосинтезирующий индикатор, включающий два семисегментных знакоместа.

- Интерфейс и разъем VGA-монитора.

- Интерфейс и разъем "мыши".

- Три разъема расширения с 42 контактами ввода-вывода каждый и семь контактов глобальных синхросигналов.

#### 2.3.1. Кнопочные переключатели микросхемы EPF10K20

Два кнопочных нефиксируемых переключателя обозначены надписями **FLEX\_PB1** и **FLEX\_PB2**. Переключатели соединены с контактами общего назначения соответственно 28 и 29 микросхемы **EPF10K20**. При нажатии переключатели замыкают указанные контакты микросхемы на общий провод через резистор 10 кОм.

# 2.3.2. Задающие переключатели микросхемы EPF10K20

Задающий DIP-переключатель **FLEX\_SW1** содержит восемь переключателей, которые позволяют задавать сигналы логического уровня на восьми многоцелевых контактах ввода-вывода микросхемы **EPF10K20**. Разомкнутое состояние выключателя соответствует логической "1", замкнутое – логическому "0". Соответствие разрядов переключателя выводам микросхемы поясняется таблицей 6.

|               | <del>_</del>   |

|---------------|----------------|

| Выключатель   | Вывод ЕРГ10К20 |

| FLEX_SWITCH-1 | 41             |

| FLEX_SWITCH-2 | 40             |

| FLEX_SWITCH-3 | 39             |

| FLEX_SWITCH-4 | 38             |

| FLEX_SWITCH-5 | 36             |

| FLEX_SWITCH-6 | 35             |

| FLEX_SWITCH-7 | 34             |

| FLEX_SWITCH-8 | 33             |

Таблица 6. Задающий DIP-переключатель FLEX\_SW1

# 2.3.3. Знакосинтезирующий индикатор микросхемы EPF10K20

Знакосинтезирующий индикатор микросхемы **EPF10K20** обозначен надписью **FLEX\_DIGIT.** Индикатор включает два знакоместа, выполненных на семисегментных индикаторах с общим катодом. Соответственно зажигание сегментов осуществляется логическим "0".

Обозначение сегментов индикаторов приведено на рис. 4. Подключение сегментов к контактам микросхемы **EPF10K20** поясняется таблицей 8.

|                  | · · · •                                                | -                                                       |

|------------------|--------------------------------------------------------|---------------------------------------------------------|

| Сегменты         | Контакты микросхемы, подключенные к первому знакоместу | Контакты микросхемы, подключенные ко второму знакоместу |

| a                | 6                                                      | 17                                                      |

| b                | 7                                                      | 18                                                      |

| c                | 8                                                      | 19                                                      |

| d                | 9                                                      | 20                                                      |

| e                | 11                                                     | 21                                                      |

| f                | 12                                                     | 23                                                      |

| g                | 13                                                     | 24                                                      |

| Десятичная точка | 14                                                     | 25                                                      |

Таблица 7. Семисегментные индикаторы микросхемы EPF10K20

# 2.3.4. Выходной адаптер и разъем VGA-монитора

Адаптер монитора VGA позволяет подавать сигналы с микросхемы **EPF10K20** на внешний монитор стандарта **VGA**.

Адаптер обеспечивает преобразование уровней логических сигналов в стандартные уровни VGA и выполнен в виде диодно-резисторной цепи.

Для подключения VGA-монитора служит стандартный 15-ти контактный разъём, обозначенный надписью VGA и включающий контакты для передачи сигналов 3-х основных цветов, а также сигналы кадровой и строчной синхронизации.

Назначение контактов разъема **VGA** и их подключение к микросхеме **EPF10K20** приведены в таблице 1. Характеристика монитора VGA дана в приложении 2.

ГУАП кафедра "Радиотехнические системы"

Контакты разъема Сигнал Выводы EPF10K20 **RED** 236 1 2 237 **GREEN BLUE** 3 238 **GND** 6,7,8,10,11 HORIZ\_SYNC 13 240 **VERT SYNC** 14 239 4,5,9,15 не задействован

Таблица 8. Контакты разъема VGA

#### 2.3.5. Входной разъем устройства "мышь"

Для ввода данных от внешних **PS/2**-устройств ("мышь", клавиатура) в микросхему **EPF10K20** служит который 6-контактный разъём типа **Mini-Din**, обозначенный надписью **Mouse**. Через этот разъем по последовательному интерфейсу от внешних устройств передаются данные, а от платы **UP1** на внешние устройства - питание.

Назначение и подключение контактов разъема приведены в таблице 9.

|             | -            |                 |

|-------------|--------------|-----------------|

| Сигнал мыши | Mini-Din Pin | Выводы ЕРГ10К20 |

| MOUSE_CLK   | 1            | 30              |

| MOUSE_DATA  | 3            | 31              |

| VCC         | 5            | -               |

| GND         | 2            | -               |

Таблица 9. Контакты разъема PS/2

# 2.3.6. Разъёмы расширения микросхемы EPF10K20

Разъемы расширения **FLEX\_EXPAN\_A**, **FLEX\_EXPAN\_B и FLEX\_EXPAN\_C** служат для подключения к микросхеме **EPF10K20** сигналов ввода-вывода, глобальных сигналов, а также питания и общего провода. Расположение и нумерация контактов разъема показаны на рис. 6.

Рис 6. Разъемы расширения микросхемы EPF10K20 на плате UP1

Таблица 10. Контакты разъема FLEX\_EXPAN\_A

| Контакт | Сигнал/контакт  | Контакт разъема | _<br>Сигнал/контакт |

|---------|-----------------|-----------------|---------------------|

| разъема | микросхемы      |                 | микросхемы          |

| 1       | RAW             | 2               | GND                 |

| 3       | VCC             | 4               | GND                 |

| 5       | VCC             | 6               | GND                 |

| 7       | не задействован | 8               | DI1/90              |

| 9       | DI2/92          | 10              | DI2/210             |

| 11      | DI4/212         | 12              | DEV_CLR/209         |

| 13      | DEV_OE/213      | 14              | DEV_CLK2/211        |

| 15      | 45              | 16              | 46                  |

| 17      | 48              | 18              | 49                  |

| 19      | 50              | 20              | 51                  |

| 21      | 53              | 22              | 54                  |

| 23      | 55              | 24              | 56                  |

| 25      | 61              | 26              | 62                  |

| 27      | 63              | 28              | 64                  |

| 29      | 65              | 30              | 66                  |

| 31      | 67              | 32              | 68                  |

| 33      | 70              | 34              | 71                  |

| 35      | 72              | 36              | 73                  |

| 37      | 74              | 38              | 75                  |

| 39      | 76              | 40              | 78                  |

| 41      | 79              | 42              | 80                  |

| 43      | 81              | 44              | 82                  |

| 45      | 83              | 46              | 84                  |

| 47      | 86              | 48              | 87                  |

| 49      | 88              | 50              | 94                  |

| 51      | 95              | 52              | 97                  |

| 53      | 98              | 54              | 99                  |

| 55      | 100             | 56              | 101                 |

| 57      | VCC             | 58              | GND                 |

| 59      | VCC             | 60              | GND                 |

Таблица 11. Контакты разъема FLEX\_EXPAN\_В

| Контакт | Сигнал/контакт  | Контакт разъема | Сигнал/контакт |

|---------|-----------------|-----------------|----------------|

| разъема | микросхемы      | _               | микросхемы     |

| 1       | RAW             | 2               | GND            |

| 3       | VCC             | 4               | GND            |

| 5       | VCC             | 6               | GND            |

| 7       | не задействован | 8               | DI1/90         |

| 9       | DI2/92          | 10              | DI2/210        |

| 11      | DI4/212         | 12              | DEV_CLR/209    |

| 13      | DEV_OE/213      | 14              | DEV_CLK2/211   |

| 15      | 109             | 16              | 110            |

| 17      | 111             | 18              | 113            |

| 19      | 114             | 20              | 115            |

| 21      | 116             | 22              | 117            |

| 23      | 118             | 24              | 119            |

| 25      | 120             | 26              | 126            |

| 27      | 127             | 28              | 128            |

| 29      | 129             | 30              | 131            |

| 31      | 132             | 32              | 133            |

| 33      | 134             | 34              | 136            |

| 35      | 137             | 36              | 138            |

| 37      | 139             | 38              | 141            |

| 39      | 142             | 40              | 143            |

| 41      | 144             | 42              | 146            |

| 43      | 147             | 44              | 148            |

| 45      | 149             | 46              | 151            |

| 47      | 152             | 48              | 153            |

| 49      | 154             | 50              | 156            |

| 51      | 157             | 52              | 158            |

| 53      | 159             | 54              | 161            |

| 55      | 162             | 56              | 163            |

| 57      | VCC             | 58              | GND            |

| 59      | VCC             | 60              | GND            |

Таблица 12. Контакты разъема FLEX\_EXPAN\_C

| Контакт<br>разъема | Сигнал/контакт<br>микросхемы | Контакт разъема | Сигнал/контакт<br>микросхемы |  |  |

|--------------------|------------------------------|-----------------|------------------------------|--|--|

| 1                  | RAW                          | 2               | GND                          |  |  |

| 3                  | VCC                          | 4               | GND                          |  |  |

| 5                  | VCC                          | 6               | GND                          |  |  |

| 7                  | не задействован              | 8               | DI1/90                       |  |  |

| 9                  | DI2/92                       | 10              | DI2/210                      |  |  |

| 11                 | DI4/212                      | 12              | DEV_CLR/209                  |  |  |

| 13                 | DEV_OE/213                   | 14              | DEV_CLK2/211                 |  |  |

| 15                 | 175                          | 16              | 181                          |  |  |

| 17                 | 182                          | 18              | 183                          |  |  |

| 19                 | 184                          | 20              | 185                          |  |  |

| 21                 | 186                          | 22              | 187                          |  |  |

| 23                 | 188                          | 24              | 190                          |  |  |

| 25                 | 191                          | 26              | 192                          |  |  |

| 27                 | 193                          | 28              | 194                          |  |  |

| 29                 | 195                          | 30              | 196                          |  |  |

| 31                 | 198                          | 32              | 199                          |  |  |

| 33                 | 200                          | 34              | 201                          |  |  |

| 35                 | 202                          | 36              | 203                          |  |  |

| 37                 | 204                          | 38              | 206                          |  |  |

| 39                 | 207                          | 40              | 208                          |  |  |

| 41                 | 214                          | 42              | 215                          |  |  |

| 43                 | 217                          | 44              | 218                          |  |  |

| 45                 | 219                          | 46              | 220                          |  |  |

| 47                 | 221                          | 48              | 222                          |  |  |

| 49                 | 223                          | 50              | 225                          |  |  |

| 51                 | 226                          | 52              | 227                          |  |  |

| 53                 | 228                          | 54              | 229                          |  |  |

| 55                 | 230                          | 56              | 231                          |  |  |

| 57                 | VCC                          | 58              | GND                          |  |  |

| 59                 | VCC                          | 60              | GND                          |  |  |

# 3. Приложение 1. Программирование и конфигурирование микросхем

Перед программированием или конфигурированием микросхем необходимо выполнить следующие действия:

- Установить режим конфигурирования с помощью соответствующих переключателей;

- Подключить кабель загрузочного устройства к параллельному порту компьютера и к разъему **JTAG\_IN** платы **UP1**;

- Установить необходимые параметры программирования/конфигурирования в САПР MAX+PLUSII.

Возможны следующие режимы конфигурирования:

- Программирование только микросхемы EPM7128S;

- Конфигурирование только микросхемы EPF10K20;

- Конфигурирование / программирование обеих микросхем

- Соединение нескольких учебных плат.

#### Программирование микросхемы семейства МАХ7000

# 1. Установка режима конфигурирования на плате UP1

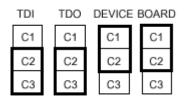

Чтобы программировать только микросхему **EPM7128S** в JTAG-цепочке, установите перемычки переключателей **TDI**, **TD0**, **DEVICE** и **BOARD** в соответствии с рисунком 7.

# Рис 7. Установка режима программирования микросхемы EPM7128S

2. Подключение загрузочного устройства ByteBlaster

Подсоедините кабель загрузки **ByteBlaster** к параллельному порту персонального компьютера и к разъёму **JTAG\_IN** на плате **UP1**.

- 3. Установка опций JTAG в пакете MAX+PLUSII

- 1. Включите **Multi-Device** в меню **JTAG** для программирования больше чем одного устройства EPM7128S.

- 2. Выберите Multi-Device в меню JTAG.

- 3. Выберите EPM7128S из списка в Device Name в диалоговом окне **Multi-Device** в меню **JTAG**.

- 4. Введите название программируемого файла для EPM7128S устройства в окне **Programming File Name**. Для просмотра директории вашего компьютера и выбора соответствующего файла может использоваться Кнопка **Select Programming**.

- 5. Нажмите **Add** для добавления устройства и программируемого файла к окну **Devices Name & Programing File Names**. Нумерация имён устройств с лева показывает порядок устройства в JTAG-цепочке. Программируемый файл устройства отображен на той же самой строке как имя устройства. Если никакой программируемый файл не связан с устройством, " <ни один> " отображен рядом с именем устройства.

- 6. Для проверки **ByteBlaster** кабеля, кода **JTAG ID** и полной инструкции JTAG-цепочки нажмите кнопку **Detect JTAG Chain Info**. Прямо над кнопкой будет выведено сообщение об обнаружении кабеля **ByteBlaster**. Вы должны вручную проверить, что это сообщение соответствует информации в окне **Devices Name & Programing File Names**.

- 7. Чтобы сохранить текущие установки **JTAG Chain File** (.jcf) нажмите **Save JCF**. В диалоговом окне **Save JCF**, введите название файла в **File Name**, и затем выберите каталог в окне каталогов, затем нажмите **OK**.

- 8. Нажмите **ОК**, чтобы сохранить ваши изменения.

- 9. Нажмите **Programm** в программаторе MAX+PLUS 11.

# Конфигурирование микросхемы семейства FLEX10K

1. Установка режима конфигурирования на плате UP1

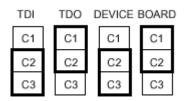

Чтобы конфигурировать только устройство EPF10K20 в JTAG-цепочке, установите перемычки переключателей **TD1**, **TD0**, **DEVICE** и **BOARD** в соответствии с рисунком 8.

# Рис 8. Установка режима конфигурирования микросхемы EPF10K20

2. Подключение загрузочного устройства ByteBlaster

Подсоедините кабель загрузки ByteBlaster к параллельному порту персонального компьютера и к разъёму JTAG\_IN на учебной плате. Для получения дополнительной информации о загрузочном кабеле «ByteBlaster», читайте описание «Загрузочный кабель «ByteBlaster» параллельного порта»

- 3. Установка опций JTAG в пакете MAX+PLUSII

- 1. Включите **Multi-Device** в меню **JTAG** для программирования более чем одного устройства EPF10K20.

- 2. Выберите Multi-Device в меню JTAG.

- 3. Выберите EPF10K20 из списка в **Device Name** в диалоговом окне **Multi-Device** в меню **JTAG**.

- 4. Введите название программируемого файла для микросхемы EPF10K20 в окне **Programming File Name**. Для просмотра директории вашего

компьютера и выбора соответствующего файла может использоваться кнопка **Select Programming**.

- 5. Нажмите **Add** для добавления устройства и программируемого файла к окну **Devices Name & Programing File Names**. Нумерация имён устройств с лева показывает порядок устройства в JTAG-цепочке. Программируемый файл устройства отображен на той же самой строке как имя устройства. Если никакой программируемый файл не связан с устройством, " <ни один> " отображен рядом с именем устройства.

- 6. Для проверки **ByteBlaster** кабеля, кода **JTAG ID** и полной инструкции JTAG-цепочки нажмите кнопку **Detect JTAG Chain Info**. Прямо над кнопкой будет выведено сообщение об обнаружении кабеля **ByteBlaster**. Вы должны вручную проверить, что это сообщение соответствует информации в окне **Devices Name & Programing File Names**.

- 7. Чтобы сохранить текущие установки **JTAG Chain File** (.jcf) нажмите **Save JCF**. В диалоговом окне **Save JCF**, введите название файла в **File Name**, и затем выберите каталог в окне каталогов, затем нажмите **OK**.

- 8. Нажмите ОК, чтобы сохранить ваши изменения.

- 9. Нажмите Configure в програматоре MAX+PLUSII.

# Совместное конфигурирование микросхем

1. Установка режима конфигурирования на плате UP1

Чтобы конфигурировать и программировать, устройства **EPF10K20** и **EPM7128S** в JTAG-цепочке, перемычки переключателей **TDI**, **TD0**, **DEVICE** и **BOARD** в соответствии с рисунком 9.

# Рис 9. Установка режима совместного конфигурирования микросхем

2. Подключение загрузочного устройства ByteBlaster

Подсоедините кабель загрузки **ByteBlaster** к параллельному порту персонального компьютера и к разъёму **JTAG\_IN** на учебной плате.

- 3. Установка опций JTAG в пакете MAX+PLUSII

- 1. Включите Multi-Device в меню JTAG.

- 2. Выберите Multi-Device в меню JTAG.

- 3. Выберите микросхему EPM7128S из списка в **Device Name** в диалоговом окне **Multi-Device** в меню **JTAG**.

- 4. Введите название программируемого файла для списка микросхем в окне **Device Name** в окне **Programming File Name**. Для просмотра директории

вашего компьютера и выбора соответствующего файла может использоваться Кнопка Select Programming.

- 5. Нажмите **Add** для добавления микросхемы и программируемого файла к окну **Devices Name & Programing File Names**. Нумерация имён устройств с лева показывает порядок микросхемы в JTAG-цепочке. Программируемый файл устройства отображен на той же самой строке как имя устройства. Если никакой программируемый файл не связан с устройством, " <ни один> " отображен рядом с именем устройства.

- 6. Повторите шаги с 3 по 5 для добавления информации для каждой микросхемы в цепочку **JTAG**.

- 7. Для проверки **ByteBlaster** кабеля, кода **JTAG ID** и полной инструкции JTAG-цепочки нажмите кнопку **Detect JTAG Chain Info**. Прямо над кнопкой будет выведено сообщение об обнаружении кабеля **ByteBlaster**. Вы должны вручную проверить, что это сообщение соответствует информации в окне **Devices Name & Programing File Names**.

- 8. Чтобы сохранить текущие установки **JTAG Chain File** (.jcf) нажмите **Save JCF**. В диалоговом окне **Save JCF**, введите название файла в **File Name**, выберите каталог в окне каталогов, затем нажмите **OK**.

- 9. Нажмите ОК, чтобы сохранить ваши изменения.

- 10. Нажмите **Configure** в програматоре MAX+PLUS II для конфигурации всех EPF10K20 устойств в цепочке **JTAG**, затем нажмите Programm для програмирования всех EPM7128S устройств в цепочке **JTAG**.

# Совместное конфигурирование нескольких плат UP1

# 1. Установка режима конфигурирования на плате UP1

Для того, чтобы конфигурировать/программировать микросхемы EPM7128S и EPF10K20 на нескольких платах **UP1**, соединенных в JTAG-цепочку, перемычки переключателей **TDI**, **TDO**, **DEVICE** и **BOARD** для всех плат, кроме последней так, в соответствии с рисунком 10.

Рис 10. Установка режима конфигурирования платы UP1 в JTAGцепочке

Последняя плата **UP1** в цепочке может конфигурировать и программировать одну или обе микросхемы. Переключатель **BOARD** должно быть установлен в соответствии с рисунком 11.

| TDI | TDO | DEVICE | BOARD |

|-----|-----|--------|-------|

| C1  | C1  | C1     | C1    |

| C2  | C2  | C2     | C2    |

| С3  | СЗ  | СЗ     | C3    |

Рис 11. Установка режима конфигурирования оконечной платы UP1

2. Подключение загрузочного устройства ByteBlaster

Подсоедините кабель загрузки ByteBlaster к параллельному порту персонального компьютера и к разъёму JTAG IN на учебной плате.

- 3. Установка опций JTAG в пакете MAX+PLUSII

- 1. Включите Multi-Device JTAG Chain в меню JTAG.

- 2. Выберите Multi-Device JTAG Chain Setup в меню JTAG.

- 3. Выберите имя первой микросхемы из списка в **Device Name** в диалоговом окне **Multi-Device JTAG Chain Setup**.

- 4. Ввести название программируемого файла для списка микросхем в окне **Device Name** в окне **Programming File Name**. Для просмотра директории вашего компьютера и выбора соответствующего программируемого файла может использоваться Кнопка **Select Programming**.

- 5. Нажмите **Add** для добавления микросхемы и программируемого файла к окну **Devices Name & Programing File Names**. Нумерация имён устройств с лева показывает порядок устройства в JTAG-цепочке. Программируемый файл устройства отображен на той же самой строке как имя устройства. Если никакой программируемый файл не связан с устройством, " <ни один> " отображен рядом с именем устройства.

- 6. Повторите шаги с 3 по 5 для добавления информации для каждого устройства в цепочку **JTAG**.

- 7. Для проверки **ByteBlaster** кабеля, кода **JTAG ID** и полной инструкции **JTAG**-цепочки нажмите кнопку **Detect JTAG Chain Info.** Прямо над кнопкой будет показано сообщение об обнаружении кабеля **ByteBlaster**. Вы должны вручную проверить, что это сообщение соответствует информации в окне **Devices Name & Programing File Names**.

- 8. Чтобы сохранить текущие установки **JTAG Chain File** (.jcf), нажмите **Save JCF**. В диалоговом окне **Save JCF**, введите название файла в **File Name**, выберите каталог в окне каталогов, затем нажмите **OK**.

- 9. Нажмите **ОК**, чтобы сохранить ваши изменения.

- 10. Нажмите **Configure** в программаторе MAX+PLUSII для конфигурирования всех EPF10K20 устройств в цепочке **JTAG**, затем нажмите **Programm** для программирования всех EPM7128S устройств в цепочке **JTAG**.

# 4. Приложение 3. Характеристика последовательного интерфейса

Последовательный интерфейс позволяет ввести данных от внешних устройств ("мышь" и клавиатура) в микросхему FLEX. Входным разъемом интерфейса служит 6-контактный разъем PS/2 mini-DIN.

Для ввода данных используется синхронный последовательный протокол. Синхронизация передачи осуществляется сигналами СLК и DATA. При отсутствии передачи СLК принимается за логическую "1", а DATA может иметь значение "0" либо "1".

Каждый такт передачи слова данных содержит стартовый бит, пакет данных, бит контроля нечетности, и стоповый бит. Стартовый бит - логический "0", стоповый бит - логическая "1". Период передачи одного слова данных составляет от 30 до 50 мкс, длительность пакета данных — от 5 до 25 мкс. Пакет данных начинается с младшего бита (DATA0 до DATA7). Формат пакета данных приведен в таблице 15.

| ,                | ,         |           | , ,       |    | , , | 1 1       |    |            |

|------------------|-----------|-----------|-----------|----|-----|-----------|----|------------|

| Packed<br>Number | <b>D7</b> | <b>D6</b> | <b>D5</b> | D4 | D3  | <b>D2</b> | D1 | <b>D</b> 0 |

| 1                | YV        | XV        | YS        | XS | 1   | 0         | R  | L          |

| 2                | X7        | X6        | X5        | X4 | X3  | X2        | X1 | X0         |

| 3                | Y7        | Y6        | Y5        | Y4 | Y3  | Y2.       | Y1 | Y0         |

Таблица 13. Формат пакета данных последовательного интерфейса

#### В таблице обозначено:

- L Left button state (состояние левой клавиши: 1 соответствует нажатию);

- **R Right button state** (состояние правой клавиши: 1 соответствует нажатию);

- **Х0-Х7** Значение перемещения по координате X;

- **Y0-Y7** Значение перемещения по координате Y;

- **XS,YS** Знак (направление) перемещения (1 отрицательное);

- **XV,YV** Выход за пределы области перемещения (1 да).

Перемещение мыши соответствует декартовой системе координат: перемещение вправо - положительно, влево - отрицательно, вверх - положительно, вниз - отрицательно. Величина движения - функция скорости движения мыши: чем быстрее движение, тем больше величина.

# 5. Приложение 2. Характеристика монитора VGA

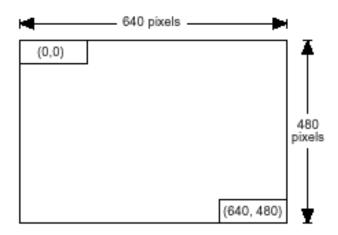

Поле отображения монитора VGA показано на рис. 12. Стандартное графическое разрешение **VGA** составляет  $640 \times 480$  пикселей (480 строк, по 640 пикселей в каждой). За начало координат поля отображения принимается его левый верхний угол с координатами (0,0).

Рис 12. Поле отображения монитора VGA

Частота видеосигнала VGA составляет 25.175 МГц, что соответствует частоте тактового генератора платы UP1.

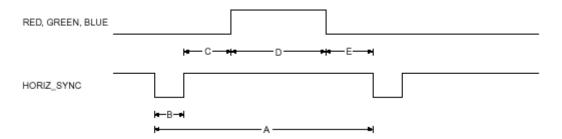

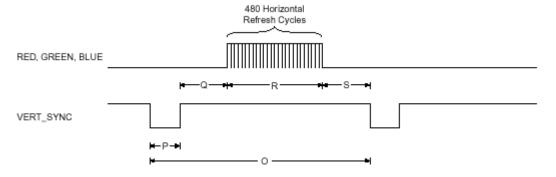

Временные диаграммы строчной и кадровой синхронизации показаны на рис. 13 и 14.

Рис 13. Временные диаграммы строчной синхронизации VGA

Рис 14. Временные диаграммы кадровой синхронизации VGA

Сигналы строчной **HORIZ\_SYNC** и кадровой **VERT\_SYNC** синхронизации подаются на генераторы сигналов горизонтальной и вертикальной разверток.

Сигналы красного, зеленого и синего цветов (**RED**, **GREEN**, **BLUE**) через соответствующие видеоусилители подаются на модуляторы (или катоды) электронных прожекторов кинескопа.

Сигналы разверток подаются на отклоняющую систему кинескопа, осуществляющую развертку телевизионного растра за счет позиционирования электронных лучей на соответствующие пиксели экрана.

Для формирования изображения сигналы красного, зеленого и синего цветов должны быть синхронизированы с положением электронных лучей на конкретных пикселях телевизионного растра.

Таблица 14. Параметры строчной синхронизации VGA

| Параметр                    | A     | В    | С    | D     | Е    |

|-----------------------------|-------|------|------|-------|------|

| Длительность интервала, мкс | 31.77 | 3.77 | 1.89 | 25.17 | 0.94 |

Таблица 15. Параметры кадровой синхронизации VGA

| Параметр                    | О    | P  | Q    | R     | S    |

|-----------------------------|------|----|------|-------|------|

| Длительность интервала, мкс | 16.6 | 64 | 1.02 | 15.25 | 0.35 |

Параметры синхронизации VGA

Период обновления пикселя определяется выражением

$$T_{pixel} = \frac{1}{f_{CLK}} = 40 \,\mu c \,,$$

(1)

где  $f_{CLK} = 25,175~M\Gamma u$  — частота видеосигнала, задаваемая тактовым генератором.

Период строчной синхронизации (период обновления строки) определяется выражением

$$T_{ROW} = A = B + C + D + E \approx 31,7 \text{ MKC},$$

(2)

$\it B$  - время строчного обратного хода луча.

$$D = T_{\text{nixel}} \times 640. \tag{3}$$

Период кадровой синхронизации (период обновления экрана) определяется выражением

$$T_{screen} = O = P + Q + R + S \approx 16,6 \,\text{MC},$$

(4)

где P — время кадрового обратного хода луча.

$$R = T_{ROW} \times 480 \tag{5}$$

# 6. Приложение 3. Пример формирования сигналов монитора VGA

Описанный функциональный узел реализуется на микросхеме семейства **FLEX** и рисует на экране монитора флаг России.

Описание проекта выполнено на языке VHDL.

Цветовая раскраска синтаксиса соответствует раскраске, используемой в текстовом редакторе пакета **MaxPlus**.

Архитектурное тело проекта включает два процесса:

- Процесс **SyncGen** формирует сигналы строчной и кадровой синхронизации VGA;

- Процесс **Video** управляет сигналами красного, зеленого и синего цветов для отображения флага России.

```

LIBRARY IEEE; -- Подключение стандартной библиотеки

USE ieee.std logic 1164.all; -- Указание на используемый пакет

ENTITY Rus_flag IS -- начало описания декларативной части

PORT

-- Debug: IN BOOLEAN;

Clock : IN std_logic; -- Внешний входной сигнал типа std_logic

HSync, VSync: OUT BOOLEAN; -- Внешние выходные сигналы

-- логического типа

vga_h_sync, vga_v_sync : OUT BOOLEAN; -- Внешние выходные

-- сигналы логического

-- типа

R, G, B: out std_logic

END Rus_flag; -- Конец описания декларативной части

ARCHITECTURE video OF Rus_flag IS -- объявление архитектуры

SIGNAL CounterY: INTEGER RANGE 0 TO 1023; --Внутренние сигналы

-- целого типа

-- разрядностью 10 бит

SIGNAL HS, VS, vga_HS, vga_VS: BOOLEAN; --Внутренние сигналы

-- логического типа

BEGIN -- Начало описания архитектуры

Syncgen: PROCESS (Clock) -- Объявление процесса

VARIABLE -- объявление переменных процесса

EnableCntY, ResetCntY: BOOLEAN;

BEGIN -- Начало описание процесса

EnableCntY := (CounterX = 40);

ResetCntY := (CounterY = 524);

IF Clock'EVENT AND Clock = '1' THEN

IF CounterX = 799 THEN

CounterX \le 0;

```

```

ELSE

CounterX <= CounterX + 1;

END IF:

IF EnableCntY THEN

IF ResetCntY THEN

CounterY \le 0;

ELSE

CounterY <= CounterY + 1;

END IF:

END IF:

vga_HS \le (CounterX < 96);

vga VS \leq (CounterY < 2);

HS \ll (CounterX = 128);

VS \ll (CounterY = 32) AND HS;

--IF DEBUG THEN CounterY <= 31; END IF;

END IF:

END PROCESS Syncgen; -- Конец описания процесса Syncgen

Video: Process(clock)

Variable Col count:integer range 0 to 1023;

Variable HS_Latch:boolean; -- Объявление Защелки Как переменной

begin

--R \le '0'; B \le '0'; G \le '0';

if(clock'EVENT and Clock='0') then

if(HS) then

HS_Latch := true; -- Установка защелки для HS

end if;

if (HS_Latch) then

Col_count := Col_count+1; -- Счетчик длительности видеополя

if((0 < Counter Y) and (Counter Y < 150)) then -- Высота белой цветной

-- полосы

if(Col_count < 630) then -- Установка белого цвета

R <= '1'; B <= '1'; G<= '1';

else

R \le 0'; B \le 0'; G \le 0';

Col count := 0; HS Latch := false;

end if:

elsif((150 < CounterY)and(CounterY < 300)) then -- Высота синей цветной

-- полосы

if(Col count < 630) then

-- Установка синего цвета

R \le 0'; B \le 1'; G \le 0';

else

R \le 0'; B \le 0'; G \le 0';

```

```

Col_count := 0; HS_Latch := false;

end if;

elsif((300 < Counter Y) \ and \ (Counter Y < 450)) \ then -- Высота красной

-- цветной полосы

if(Col_count < 630) then -- Устанока красного цвета

R \le '1'; B \le '0'; G \le '0';

else

R \le 0'; B \le 0': G \le 0';

Col_count := 0; HS_Latch := false;

end if;

else R<= '0'; B <= '0'; G <= '0';

end if;

end if;

end if:

end Process Video;

-- Присвоение значений внутренних сигналов внешним выходным сигналам

vga_h_sync <= vga_HS;</pre>

vga_v_sync <= vga_VS;</pre>

HSync <= HS;

VSync <= VS;

END video;

```

#### 7. Глоссарий

| •                        | <b>BST</b> | Boundary | Scan | Test | (тестовое | периферийное | сканирова- |  |  |

|--------------------------|------------|----------|------|------|-----------|--------------|------------|--|--|

| ние цифровых устройств). |            |          |      |      |           |              |            |  |  |

- **ByteBlaster** ...... устройство и кабель загрузки конфигурирующих данных в микросхемы Altera через параллельный порт компьютера.

- **EPC**..... Erasable Configuration PROM (конфигурационное ППЗУ).

- **FLEX**......Flexible Logic Element Matrix (матрица элементов гибкой логики).

- **JTAG**...... Joint Test Action Group (объединенная группа по вопросам тестирования цифровых схем).

- MAX......Multiple Array Matrix (матрица множественных массивов логических элементов).

- PLCC......Plastic J-lead Chip Carrier (пластиковый корпус с выводами J-формы).

- **PROM** ...... Programmable Read Only Memory (программируемое ПЗУ).

- **TAP**.....Тest Access Port (порт тестирования JTAG).

- **TCK**..... Test Clock (тактовый вход JTAG).

- **TDI** ..... Test Data Input (вход тестовых данных JTAG).

- TDO..... Test Data Output (выход тестовых данных JTAG).

- **TMS**...... Test Mashine State Control (управление конечным автоматом JTAG).

- VGA..... Video Graphics Array (графическое видеоотображение).

- ПЗУ .....постоянное запоминающее устройство.

- ПЛИС ..... программируемая логическая интегральная схема.