# RM0008 Reference manual STM32F101xx, STM32F102xx, STM32F103xx, STM32F105xx and STM32F107xx advanced Arm<sup>®</sup>-based 32-bit MCUs

# Руководство

Пересказал А. Косенко aikos55@gmail.com

1

<sup>&</sup>lt;sup>1</sup> Кому не лень, проставьте ссылки оглавления сами.

| 1. | Введение                                                                                      | 17        |

|----|-----------------------------------------------------------------------------------------------|-----------|

| 2. | Типографские соглашения                                                                       | 19        |

|    | 2.1. Сокращения для регистров                                                                 | 19        |

|    | 2.2. Словарь                                                                                  | 20        |

| _  | 2.3. Доступность периферии                                                                    | 20        |

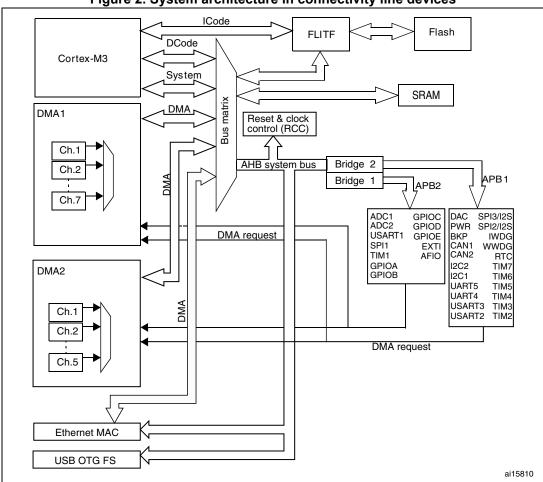

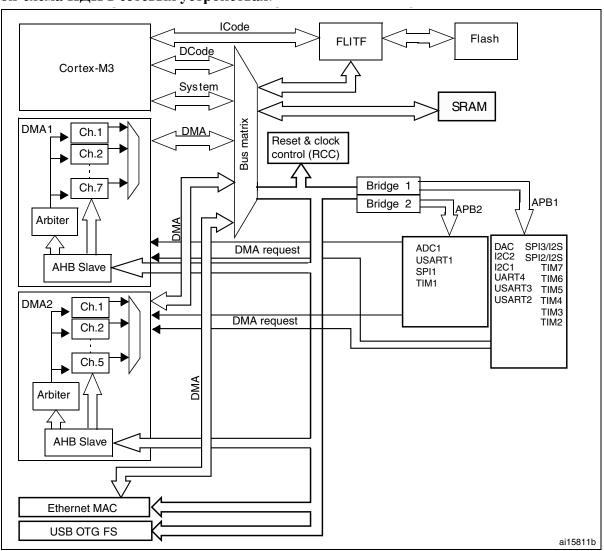

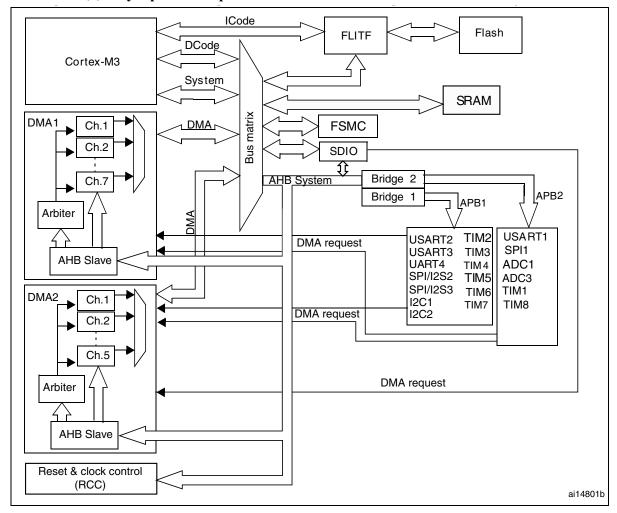

| 3. | . Архитектура памяти и шины                                                                   | 20        |

|    | 3.1. Архитектура системы                                                                      | 20        |

|    | 3.2. Организация памяти<br>3.3. Карта памяти                                                  | 23<br>23  |

|    | 3.3.1. Встроенная SRAM                                                                        | 25<br>25  |

|    | 3.3.2. Атомарный доступ                                                                       | 25        |

|    | 3.3.3. Встроенная флэш память                                                                 | 25        |

|    | 3.4. Конфигурация загрузки                                                                    | 32        |

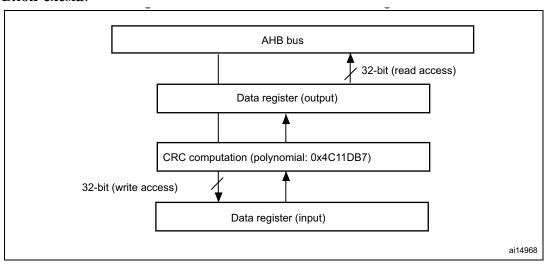

| 4. | Блок вычисления CRC                                                                           | 33        |

|    | 4.1. Введение в CRC                                                                           | 33        |

|    | 4.2. Основные свойства СRC                                                                    | 33        |

|    | 4.3. Функциональное описание CRC<br>4.4. Регистры CRC                                         | 33<br>33  |

|    | 4.4.1. Регистр данных (CRC_DR)                                                                | 34        |

|    | 4.4.2. Независимый регистр данных (CRC_IDR)                                                   | 34        |

|    | 4.4.3. Регистр управления (CRC_CR)                                                            | 34        |

|    | 4.4.4. Карта регистров CRC                                                                    | 34        |

| 5. | •                                                                                             | 35        |

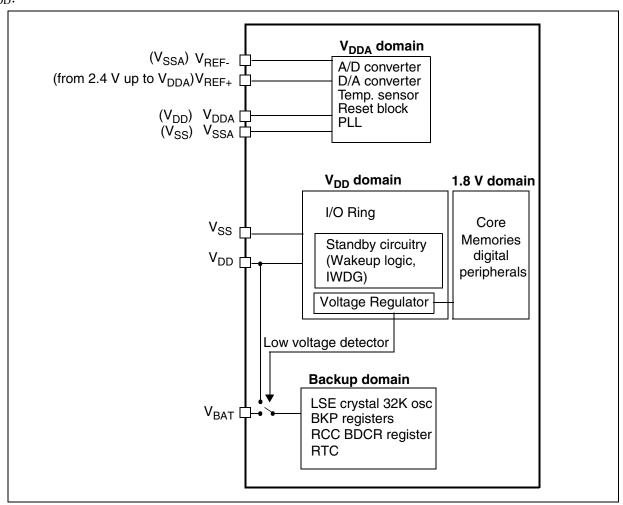

|    | 5.1. Источники питания                                                                        | 35        |

|    | 5.1.1. Независимое питание ADC и DAC и опорное напряжение 5.1.2. Резервное батарейное питание | 35<br>36  |

|    | 5.1.3. Регулятор напряжения                                                                   | 36        |

|    | 5.2. Супервизор питания                                                                       | 36        |

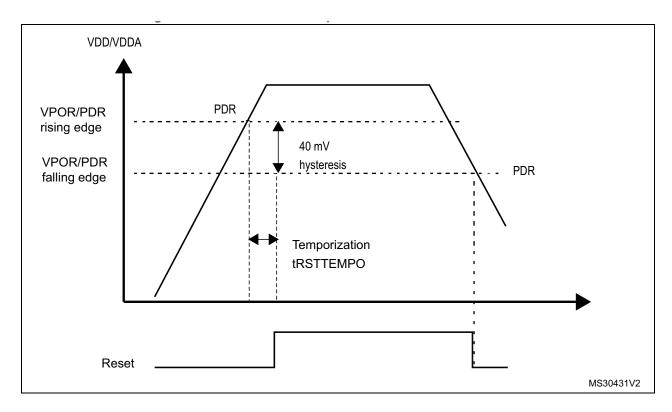

|    | 5.2.1. Сброс по включению (POR)/сброс по выключению (PDR)                                     | 36        |

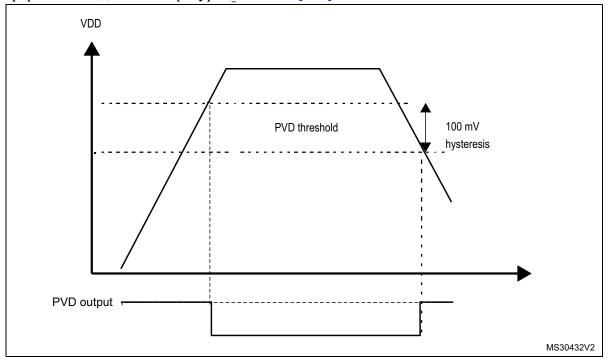

|    | 5.2.2. Программируемый детектор напряжения (PVD)                                              | 37        |

|    | 5.3. Режимы пониженного потребления 5.3.1. Замедление системных тактов                        | 37<br>38  |

|    | 5.3.2. Выключение тактов периферии                                                            | 38        |

|    | 5.3.3. Режим сна                                                                              | 38        |

|    | 5.3.4. Режим остановки                                                                        | 39        |

|    | 5.3.5. Дежурный режим 5.3.6. Автопробуждение (AWU) из экономного режима                       | 40<br>41  |

|    | 5.4. Регистры управления питанием                                                             | 41        |

|    | 5.4.1. Регистр управления (PWR_CR)                                                            | 41        |

|    | 5.4.2. Регистр состояния и управления (PWR_CSR)                                               | 42        |

|    | 5.4.3. Карта регистров PWR                                                                    | 43        |

| 6. | Регистры резервного хранения ВКР                                                              | 43        |

|    | 6.1. Введение в ВКР                                                                           | 43        |

|    | 6.2. Основные свойства ВКР                                                                    | 43        |

|    | 6.3. Описание работы ВКР 6.3.1. Обнаружение вмешательства (Tamper)                            | 43<br>43  |

|    | 6.3.2. Калибровка RTC                                                                         | 44        |

|    | 6.4. Регистры BKP                                                                             | 44        |

|    | 6.4.1. Регистры данных (ВКР_DRx) (x = 142)                                                    | 44        |

|    | 6.4.2. Регистр калибровки RTC (BKP_RTCCR)                                                     | 44<br>44  |

|    | 6.4.3. Регистр управления ВКР (ВКР_СR)<br>6.4.4. Регистр управления/состояния ВКР (ВКР_CSR)   | 44<br>45  |

| 7. |                                                                                               | 45        |

| 1. | 7.1. Сброс                                                                                    | <b>45</b> |

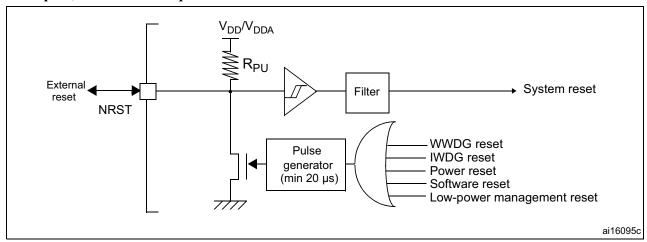

|    | 7.1.1. Системный сброс                                                                        | 45        |

|    |         | Сорос питания                                                                                       | 40       |

|----|---------|-----------------------------------------------------------------------------------------------------|----------|

|    |         | Сброс резервного домена                                                                             | 46       |

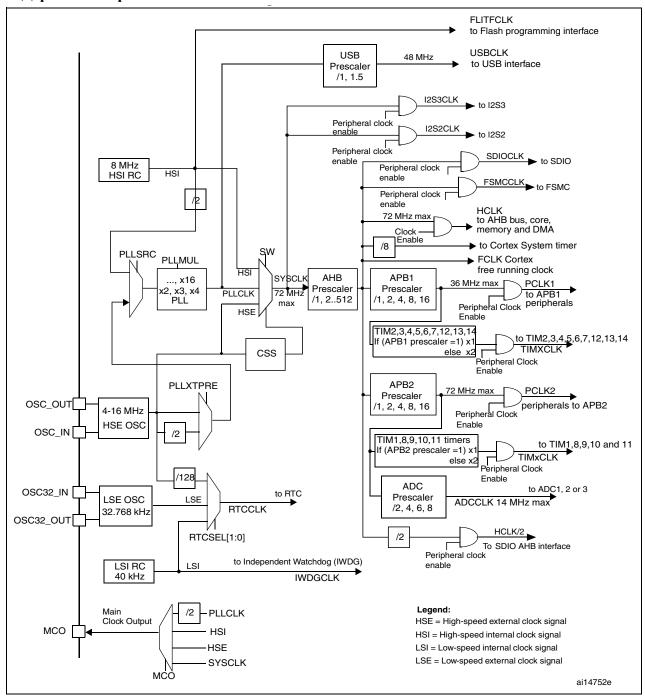

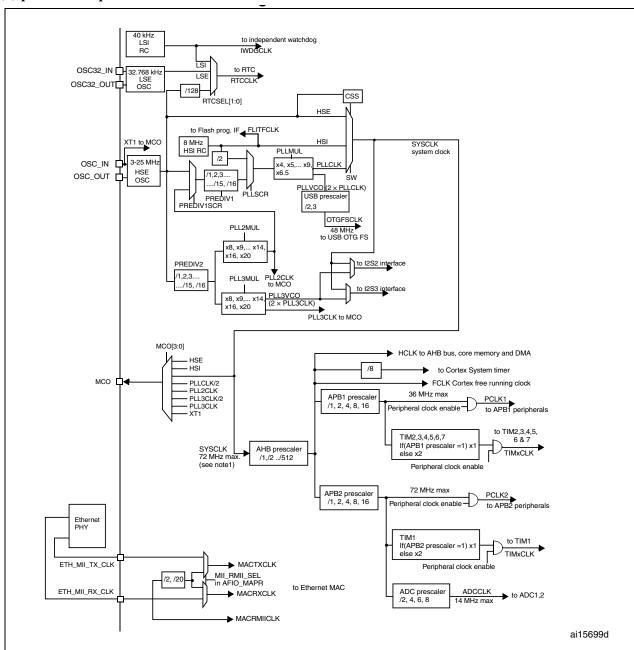

|    | 7.2. Ta | ктирование                                                                                          | 46       |

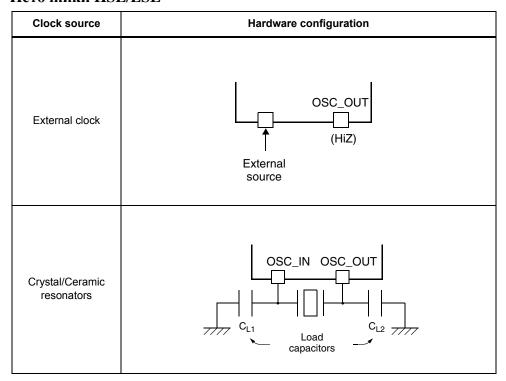

|    | 7.2.1.  | Такты HSE                                                                                           | 48       |

|    | 7.2.2.  | Такты HSI                                                                                           | 49       |

|    | 7.2.3.  | PLL (ΦΑΠԿ)                                                                                          | 49       |

|    |         | Такты LSE                                                                                           | 49       |

|    |         | Такты LSI                                                                                           | 49       |

|    |         | Выбор SysClk                                                                                        | 50       |

|    |         | Система безопасности тактирования (CSS)                                                             | 50       |

|    |         | Такты RTC                                                                                           | 50       |

|    |         |                                                                                                     | 50       |

|    |         | Такты сторожевого таймера                                                                           |          |

|    |         | Вывод тактового сигнала                                                                             | 50       |

|    |         | гистры RCC                                                                                          | 51       |

|    | 7.3.1.  | Регистр управления (RCC_CR)                                                                         | 51       |

|    | 7.3.2.  | Регистр конфигурации (RCC_CFR)                                                                      | 52       |

|    | 7.3.3.  | Регистр прерываний (RCC_CIR)                                                                        | 54       |

|    | 7.3.4.  | Регистр сброса периферии APB2 (RCC_APB2RSTR)                                                        | 55       |

|    | 7.3.5.  | Регистр сброса периферии APB1 (RCC_APB1RSTR)                                                        | 55       |

|    | 7.3.6.  | Регистр разрешения тактов периферии AHB (RCC_AHBENR)                                                | 56       |

|    |         | Регистр разрешения тактов периферии APB2 (RCC_APB2ENR)                                              | 57       |

|    |         | Регистр разрешения тактов периферии APB1 (RCC_APB1ENR)                                              | 57       |

|    |         | Регистр управления резервным доменом (RCC_BDCR)                                                     | 58       |

|    |         | Регистр состояния/управления (RCC_CSR)                                                              | 59       |

|    |         | Карта регистров RCC                                                                                 | 61       |

|    |         | Napra pervicipos noo                                                                                |          |

| 8. | Сете    | вые устройства: сброс и тактирование                                                                | 62       |

|    | 8.1. C6 | DOC                                                                                                 | 62       |

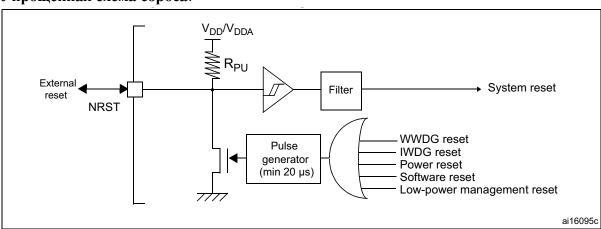

|    |         | Системный сброс                                                                                     | 62       |

|    |         | Сброс питания                                                                                       | 62       |

|    |         | Сброс резервного домена                                                                             | 63       |

|    |         |                                                                                                     |          |

|    |         | ктирование                                                                                          | 63       |

|    |         | Такты HSE                                                                                           | 64       |

|    |         | Такты HSI                                                                                           | 65       |

|    | 8.2.3.  |                                                                                                     | 65       |

|    | _       | Такты LSE                                                                                           | 66       |

|    |         | Такты LSI                                                                                           | 66       |

|    |         | Выбор SysClk                                                                                        | 66       |

|    |         | Система безопасности тактирования (CSS)                                                             | 66       |

|    | 8.2.8.  | Такты RTC                                                                                           | 67       |

|    | 8.2.9.  | Такты сторожевого таймера                                                                           | 67       |

|    | 8.2.10. | Вывод тактового сигнала                                                                             | 67       |

|    | 8.3. Pe | гистры RCC                                                                                          | 67       |

|    | 8.3.1.  | ·                                                                                                   | 67       |

|    | 8.3.2.  | Регистр конфигурации (RCC_CFGR)                                                                     | 69       |

|    |         | Регистр прерываний (RCC_CIR)                                                                        | 71       |

|    |         | Регистр прерывании (Nee_ont) Регистр сброса периферии APB2 (RCC_APB2RSTR)                           | 72       |

|    |         | Регистр сброса периферии APB1 (RCC_APB1RSTR)                                                        | 72       |

|    |         | Регистр сороса периферии AI ВТ (ПСС_AI ВТПЗТТ) Регистр разрешения тактов периферии AHB (RCC_AHBENR) | 73       |

|    | 8.3.7.  |                                                                                                     | 73       |

|    |         |                                                                                                     |          |

|    | 8.3.8.  |                                                                                                     | 74       |

|    | 8.3.9.  | · · · · · · · · · · · · · · · · · · ·                                                               | 75       |

|    |         | Регистр состояния/управления (RCC_CSR)                                                              | 76       |

|    |         | Регистр сброса периферии AHB (RCC_AHBRSTR)                                                          | 77       |

|    |         | Второй регистр конфигурации (RCC_CFGR2)                                                             | 77       |

|    | 8.3.13. | Карта регистров RCC                                                                                 | 79       |

| 9. | Попт    | ы и альтернативные функции (GPIO и AFIO)                                                            | 80       |

| ٠. |         |                                                                                                     |          |

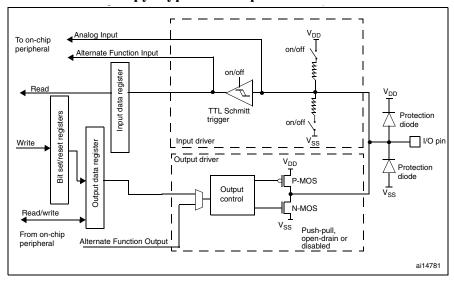

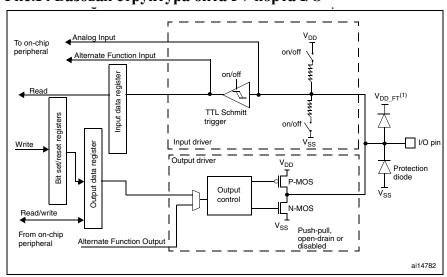

|    | _       | бота GPIO                                                                                           | 80<br>81 |

|    | 911     | Вв/Выв общего назначения (GPIO)                                                                     | الا<br>1 |

| 9.1.2. Атомарная установка и снятие битов                                                                                 | 81         |

|---------------------------------------------------------------------------------------------------------------------------|------------|

| 9.1.3. Внешние линии прерывания/побудки                                                                                   | 81         |

| 9.1.4. Альтернативные функции (АF)                                                                                        | 82         |

| 9.1.5. Программное перенаправление альтернативных функций                                                                 | 82         |

| 9.1.6. Механизм блокировки GPIO                                                                                           | 82         |

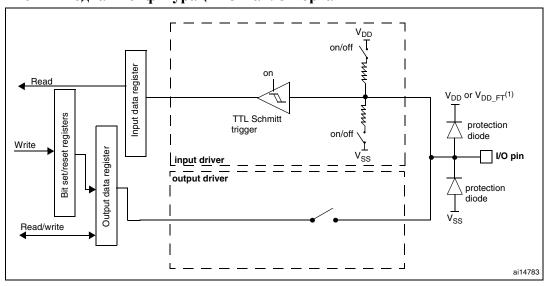

| 9.1.7. Конфигурация ввода                                                                                                 | 82         |

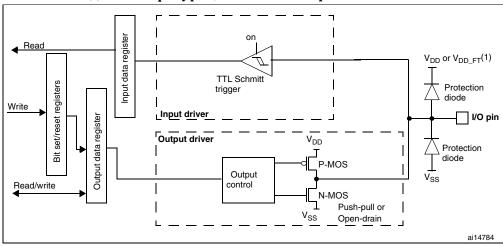

| 9.1.8. Конфигурация вывода                                                                                                | 83         |

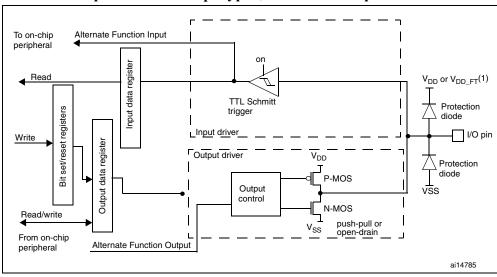

| 9.1.9. Конфигурация альтернативных функций                                                                                | 83         |

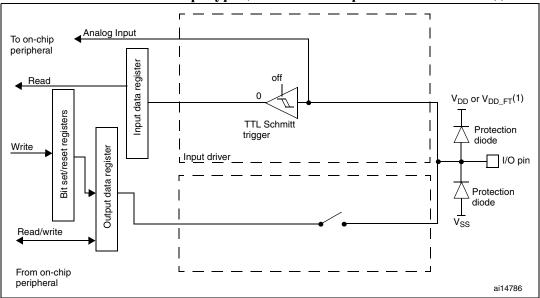

| 9.1.10. Аналоговая конфигурация                                                                                           | 84         |

| 9.1.11. Конфигурация GPIO для периферии                                                                                   | 84         |

| 9.2. Peructpu GPIO                                                                                                        | 88         |

| 9.2.1. Младший регистр конфигурации порта (GPIOx_CRL) (x=AG) 9.2.2. Старший регистр конфигурации порта (GPIOx_CRH) (x=AG) | 88<br>88   |

| 9.2.3. Регистр данных ввода порта (GPIOx_IDR) (x=AG)                                                                      | 89         |

| 9.2.4. Регистр данных вывода порта (GPIOx_ODR) (x=AG)                                                                     | 89         |

| 9.2.5. Регистр установки/сброса битов порта (GPIOx_BSRR) (x=AG)                                                           | 89         |

| 9.2.6. Регистр сброса битов порта (GPIOx_BRR) (x=AG)                                                                      | 90         |

| 9.2.7. Регистр блокировки конфигурации порта (GPIOx_LCRR) (x=AG)                                                          | 90         |

| 9.3. Альтернативный IO и конфигурация отладки (AFIO)                                                                      | 91         |

| 9.3.1. Ножки OSC32_IN/OSC32_OUT как GPIO PC14/PC15                                                                        | 91         |

| 9.3.2. Ножки OSC_IN/OSC_OUT как GPIO PD0/PD1                                                                              | 91         |

| 9.3.3. Перенаправление CAN1                                                                                               | 91         |

| 9.3.4. Перенаправление CAN2                                                                                               | 91         |

| 9.3.5. Перенаправление JTAG/SWD                                                                                           | 91         |

| 9.3.6. Перенаправление ADC                                                                                                | 92         |

| 9.3.7. Перенаправление таймеров                                                                                           | 93         |

| 9.3.8. Перенаправление USART                                                                                              | 95         |

| 9.3.9. Перенаправление I2C1                                                                                               | 95         |

| 9.3.10. Перенаправление SPI1                                                                                              | 95         |

| 9.3.11. Перенаправление SPI3/I2S3                                                                                         | 96         |

| 9.3.12. Перенаправление Ethernet                                                                                          | 96         |

| 9.4. Peructpu AFIO                                                                                                        | 96         |

| 9.4.1. Регистр управления событием (AFIO_EVCR)                                                                            | 96<br>97   |

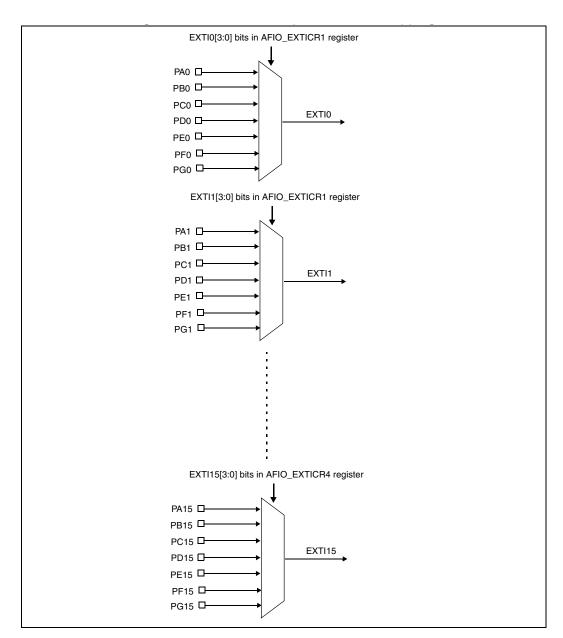

| 9.4.2. Регистр картирования АF и отладки (AFIO_MAPR) 9.4.3. Регистр 1 конфигурации внешнего прерывания (AFIO_EXTICR1)     | 101        |

| 9.4.4. Регистр 1 конфигурации внешнего прерывания (AFIO_EXTICR2)                                                          | 101        |

| 9.4.5. Регистр 2 конфигурации внешнего прерывания (AFIO_EXTICR3)                                                          | 101        |

| 9.4.6. Регистр 4 конфигурации внешнего прерывания (AFIO EXTICR4)                                                          | 102        |

| 9.4.7. Регистр 2 картирования АF и отладки (AFIO_MAPR2)                                                                   | 102        |

| 9.5. Карта регистров GPIO и AFIO                                                                                          | 103        |

| • • •                                                                                                                     |            |

| 10. Прерывания и события                                                                                                  | 105        |

| 10.1. Контроллер вложенных прерываний (NVIC)                                                                              | 105        |

| 10.1.1. Регистр калибровки SysTick                                                                                        | 105        |

| 10.1.2. Векторы прерываний и исключений                                                                                   | 105        |

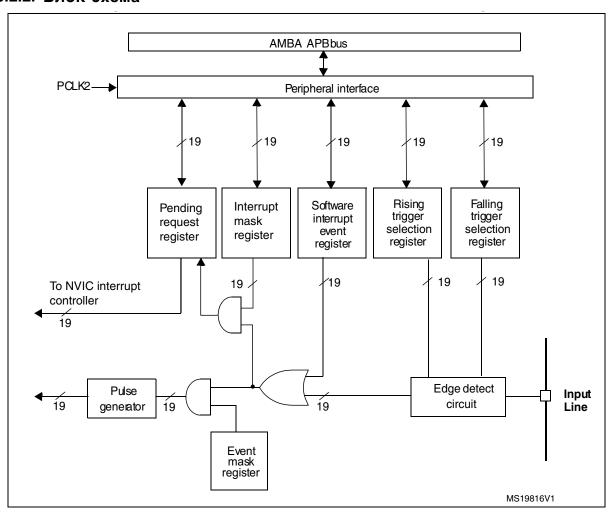

| 10.2. Контроллер внешних прерываний/событий (EXTI)                                                                        | 112        |

| 10.2.1. Основные свойства                                                                                                 | 112        |

| 10.2.2. Блок-схема<br>10.2.3. Событие побудки                                                                             | 112<br>113 |

| 10.2.3. Сообтие пооудки<br>10.2.4. Функциональное описание                                                                | 113        |

| 10.2.5. Подключение линий внешних событий/прерываний                                                                      | 113        |

| ···                                                                                                                       | 114        |

| 10.3. Регистры EXTI<br>10.3.1. Регистр маски прерывания (EXTI_IMR)                                                        | 114        |

| 10.3.1. Регистр маски прерывания (EXTI_IMIA)<br>10.3.2. Регистр маски события (EXTI_EMR)                                  | 115        |

| 10.3.3. Регистр маски сообтин (EXTI_EMT)  10.3.3. Регистр выбора переднего фронта запуска (EXTI_RTSR)                     | 115        |

| 10.3.4. Регистр выбора нереднего фронта запуска (EXTI_RTSR)                                                               | 115        |

| 10.3.5. Регистр программного события/прерывания (EXTI_SWIER)                                                              | 116        |

| 10.3.6. Регистр удержания (EXTI_PR)                                                                                       | 116        |

| 10.3.7. Карта регистров EXTI_PR                                                                                           | 117        |

| · · · —                                                                                                                   |            |

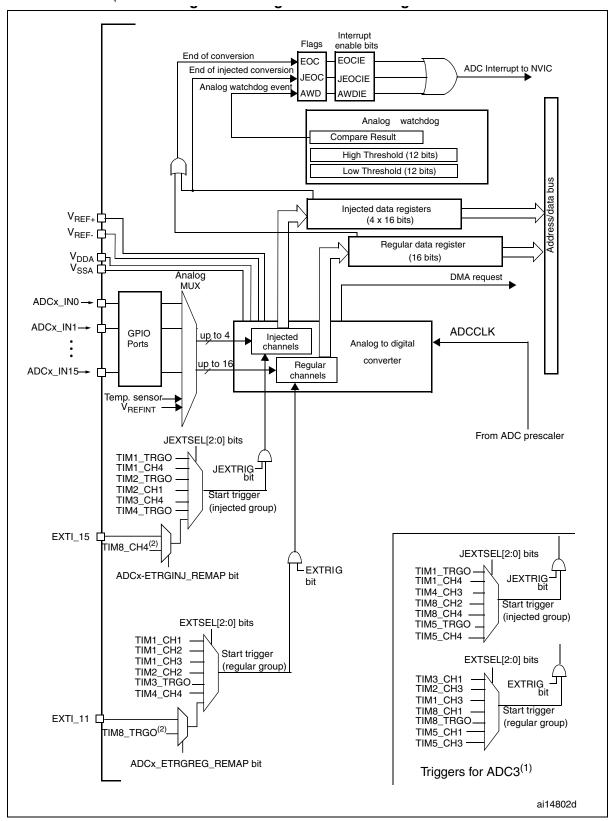

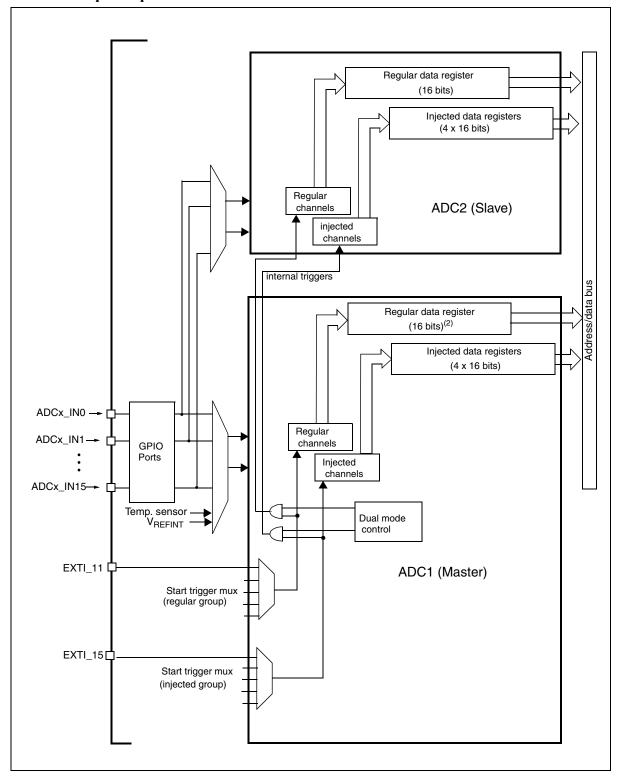

| 11. Аналого-цифровой преобразователь (ADC)                                                              | 117        |

|---------------------------------------------------------------------------------------------------------|------------|

| 11.1. Введение в АЦП                                                                                    | 117        |

| 11.2. Основные свойства АЦП                                                                             | 117        |

| 11.3. Функциональное описание АЦП                                                                       | 118        |

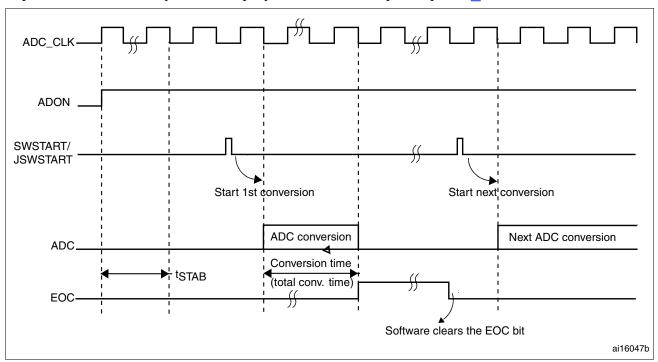

| 11.3.1. Вкл./Выкл. АЦП                                                                                  | 119        |

| 11.3.2. Такты АЦП                                                                                       | 119        |

| 11.3.3. Выбор канала                                                                                    | 119        |

| 11.3.4. Одинарное преобразование                                                                        | 119        |

| 11.3.5. Непрерывное преобразование                                                                      | 120        |

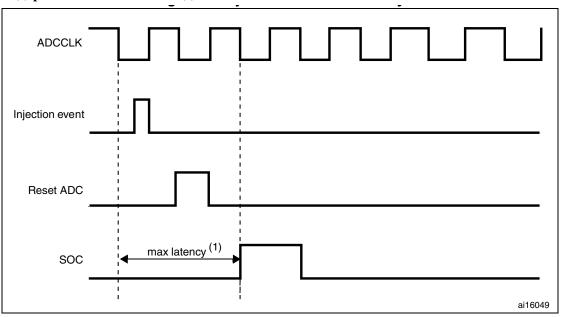

| 11.3.6. Временная диаграмма                                                                             | 120        |

| 11.3.7. Аналоговый сторож                                                                               | 120        |

| 11.3.8. Режим сканирования                                                                              | 121        |

| 11.3.9. Управление вставными каналами                                                                   | 121        |

| 11.3.10.Прерывный режим                                                                                 | 122        |

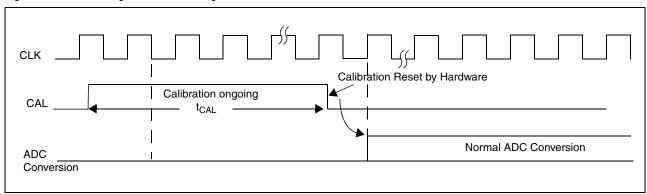

| 11.4. Калибровка                                                                                        | 123        |

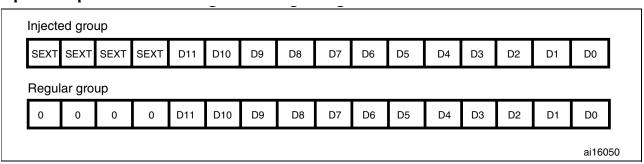

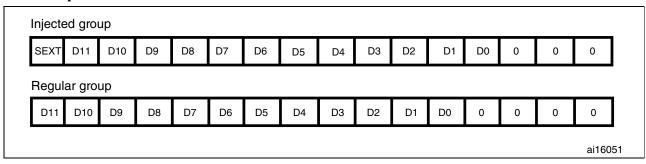

| 11.5. Выравнивание данных                                                                               | 123        |

| 11.6. Время выборки каналов                                                                             | 124        |

| 11.7. Внешний запуск преобразования                                                                     | 124        |

| 11.8. Запрос DMA                                                                                        | 125        |

| 11.9. Парный режим АЦП                                                                                  | 125        |

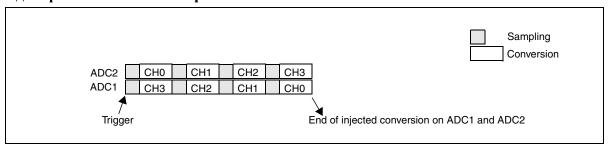

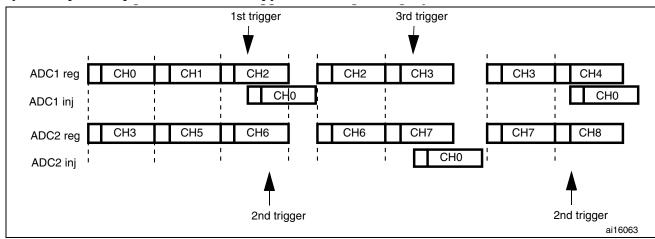

| 11.9.1. Вставной одновременный режим                                                                    | 127        |

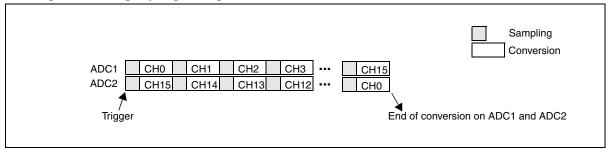

| 11.9.2. Регулярный одновременный режим                                                                  | 127        |

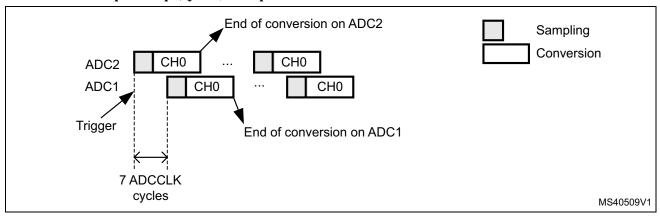

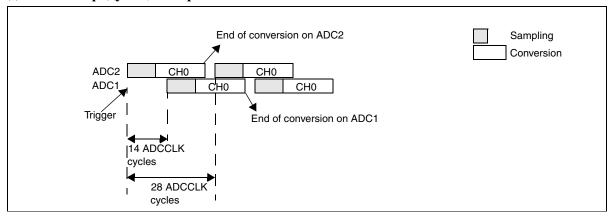

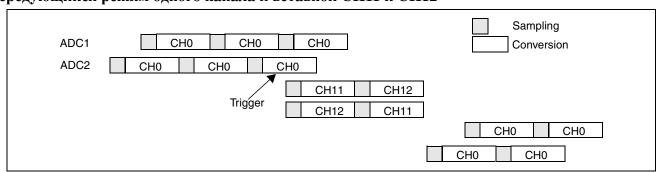

| 11.9.3. Быстрый чередующийся режим                                                                      | 127        |

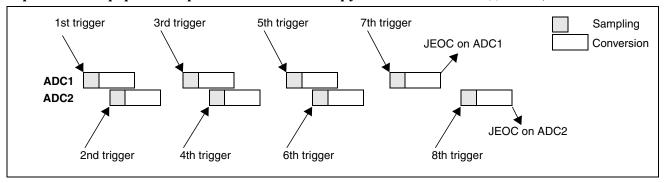

| 11.9.4. Медленный чередующийся режим                                                                    | 128        |

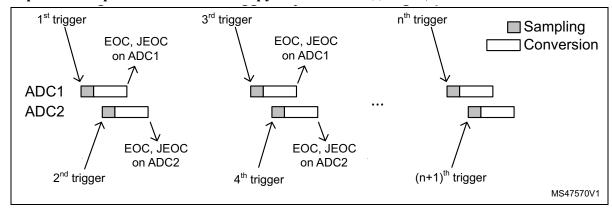

| 11.9.5. Режим попеременного запуска                                                                     | 128        |

| 11.9.6. Независимый режим                                                                               | 129        |

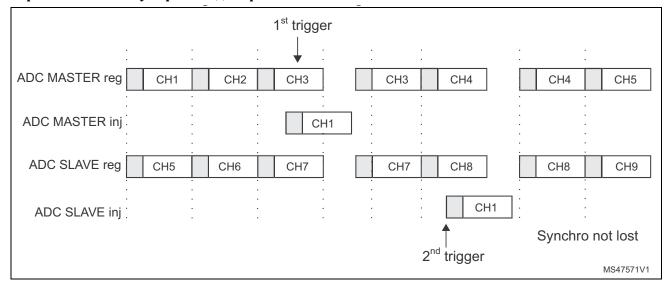

| 11.9.7. Комбинированный регулярно/вставной одноврем 11.9.8. Регулярный одновременный + Попеременный рег |            |

| 11.9.9. Вставной одновременный + Чередующийся режи                                                      |            |

|                                                                                                         |            |

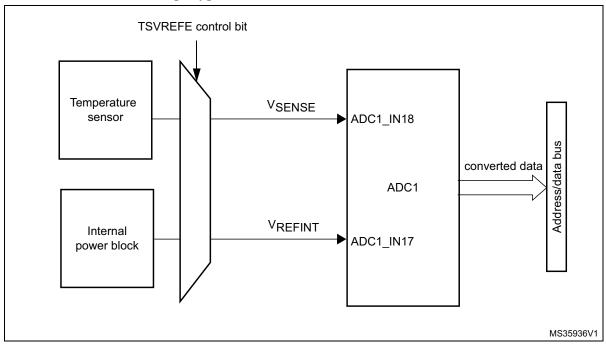

| 11.10. Датчик температуры                                                                               | 131        |

| 11.11. Прерывания АЦП                                                                                   | 131        |

| 11.12. Регистры АЦП                                                                                     | 132        |

| 11.12.1.Регистр состояния АЦП (ADC_SR)                                                                  | 132        |

| 11.12.2.Регистр 1 управления АЦП (ADC_CR1)<br>11.12.3.Регистр 2 управления АЦП (ADC_CR2)                | 132<br>134 |

| 11.12.3. Регистр 2 управления АЦГГ (ADC_Ch2) 11.12.4.Регистр 1 времени выборки АЦП (ADC_SMPR1)          | 136        |

| 11.12.5.Регистр 1 времени высорки АЦП (ADC_SMPR2)                                                       | 136        |

| 11.12.6.Смещение данных вставных каналов АЦП (АDC_                                                      |            |

| 11.12.7.Верхний порог аналогового сторожа (ADC HTR)                                                     | 137        |

| 11.12.8.Нижний порог аналогового сторожа (ADC_LTR)                                                      | 137        |

| 11.12.9.Регистр 1 регулярной последовательности (ADC_                                                   |            |

| 11.12.10.Регистр 2 регулярной последовательности (АДС                                                   |            |

| 11.12.11.Регистр 3 регулярной последовательности (АОС                                                   | •          |

| 11.12.12.Регистр вставной последовательности (ADC_JS                                                    |            |

| 11.12.13.Регистры х данных вставных каналов (ADC_JDF                                                    | · ·        |

| 11.12.14.Регистр данных регулярных каналов (ADC_DR)                                                     | 140        |

| 11.12.15.Карта регистров АЦП                                                                            | 140        |

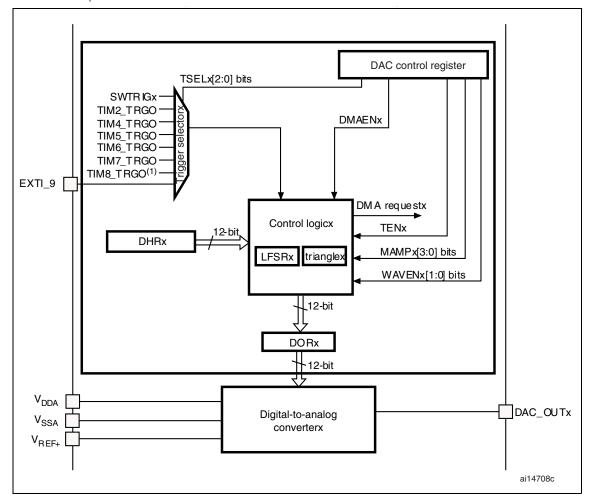

| 12. Цифро-аналоговый преобразователь (DAC)                                                              | 141        |

| 12.1. Введение в ЦАП                                                                                    | 141        |

| 12.2. Основные свойства ЦАП                                                                             | 141        |

| 12.3. Основные свойства ЦАП                                                                             | 142        |

| 12.3.1. Включение канала ЦАП                                                                            | 142        |

| 12.3.2. Включение выходных буферов ЦАП                                                                  | 142        |

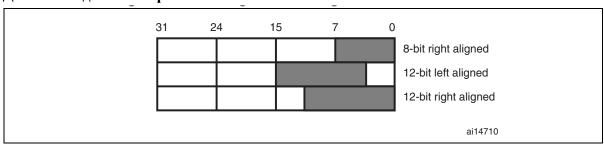

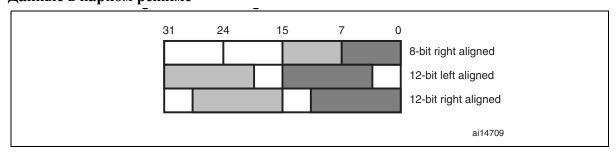

| 12.3.3. Формат данных ЦАП                                                                               | 143        |

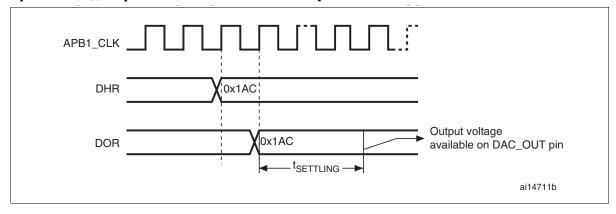

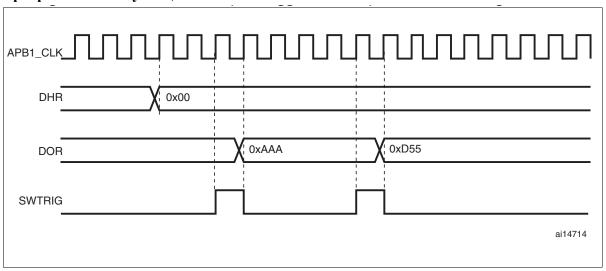

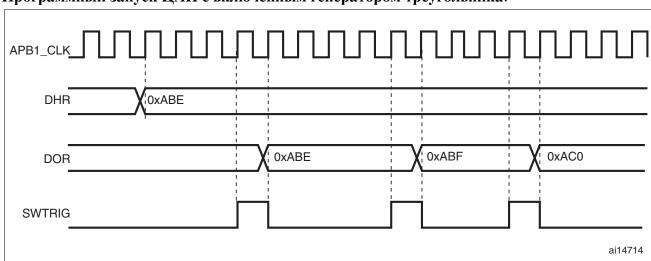

| 12.3.4. Преобразование ЦАП                                                                              | 143        |

| 12.3.5. Выходное напряжение ЦАП                                                                         | 144        |

| 12.3.6. Выбор запуска ЦАП                                                                               | 144        |

| 12.3.7. Запрос DMA                                                                                      | 144        |

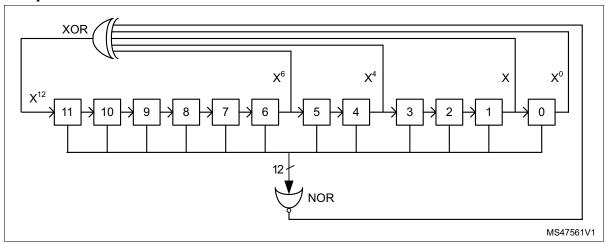

| 12.3.8. Генерация шума                                                                                  | 145        |

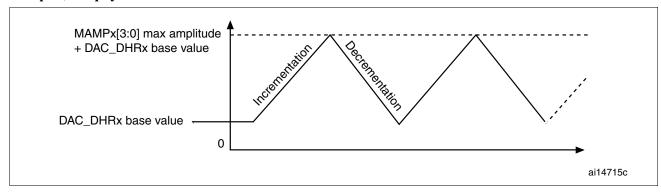

| 12.3.9. Генерация треугольного сигнала                                                                                                                                                                                                      | 145                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 12.4. Парный режим ЦАП                                                                                                                                                                                                                      | 146                                                  |

| 12.4.1. Независимый запуск ЦАП без генераторов                                                                                                                                                                                              | 146                                                  |

| 12.4.2. Независимый запуск ЦАП с одинаковым LFSR                                                                                                                                                                                            | 146                                                  |

| 12.4.3. Независимый запуск ЦАП с разными LFSR                                                                                                                                                                                               | 147                                                  |

| 12.4.4. Независимый запуск ЦАП с одинаковым треугольным сигналом                                                                                                                                                                            | 147                                                  |

| 12.4.5. Независимый запуск ЦАП с разным треугольным сигналом                                                                                                                                                                                | 147                                                  |

| 12.4.6. Одновременный программный запуск ЦАП                                                                                                                                                                                                | 147                                                  |

| 12.4.7. Одновременный запуск ЦАП без генераторов                                                                                                                                                                                            | 147                                                  |

| 12.4.8. Одновременный запуск ЦАП с одинаковым LFSR                                                                                                                                                                                          | 148                                                  |

| 12.4.9. Одновременный запуск ЦАП с разными LFSR                                                                                                                                                                                             | 148                                                  |

| 12.4.10.Одновременный запуск ЦАП с одинаковым треугольным сигналом                                                                                                                                                                          | 148                                                  |

| 12.4.11.Одновременный запуск ЦАП с разным треугольным сигналом                                                                                                                                                                              | 148                                                  |

| 12.5. Регистры ЦАП                                                                                                                                                                                                                          | 149                                                  |

| 12.5.1. Регистры ддіт<br>12.5.1. Регистр управления АЦП (ADC_CR)                                                                                                                                                                            | 149                                                  |

| 12.5.2. Регистр программного запуска АЦП (ADC_SWTRIGR)                                                                                                                                                                                      | 151                                                  |

| 12.5.3. Регистр хранения правых 12-бит данных канала 1 (DAC_DHR12R1)                                                                                                                                                                        | 151                                                  |

| 12.5.4. Регистр хранения левых 12-бит данных канала 1 (DAC_DHR12L1)                                                                                                                                                                         | 151                                                  |

| 12.5.5. Регистр хранения правых 8-бит данных канала 1 (DAC_DHR8R1)                                                                                                                                                                          | 152                                                  |

| 12.5.6. Регистр хранения правых 12-бит данных канала 2 (DAC_DHR12R2)                                                                                                                                                                        | 152                                                  |

| 12.5.7. Регистр хранения правых 12-бит данных канала 2 (DAC_DHR12L2)                                                                                                                                                                        | 152                                                  |

| 12.5.8. Регистр хранения правых 8-бит данных канала 2 (DAC_DHR8R2)                                                                                                                                                                          | 152                                                  |

| 12.5.9. Парный регистр правых 0-бит данных канала 2 (DAC_DITITION2)                                                                                                                                                                         | 153                                                  |

|                                                                                                                                                                                                                                             | 153                                                  |

| 12.5.10.Парный регистр левых 12-бит данных (DAC_DHL12RD)<br>12.5.11.Парный регистр правых 8-бит данных (DAC_DHR8RD)                                                                                                                         | 153                                                  |

| 12.5.11. Парный регистр правых о-ойт данных (DAC_DITHORD) 12.5.12.Выходной регистр данных канала 1 (DAC_DOR1)                                                                                                                               | 153                                                  |

| 12.5.12.Выходной регистр данных канала 1 (DAC_DON1) 12.5.13.Выходной регистр данных канала 2 (DAC_DOR2)                                                                                                                                     | 154                                                  |

| 12.5.13.Быходной регистр данных канала 2 (DAC_DOn2)<br>12.5.14.Карта регистров ЦАП                                                                                                                                                          | 154                                                  |

| 12.3.14. Карта регистров цип                                                                                                                                                                                                                | 134                                                  |

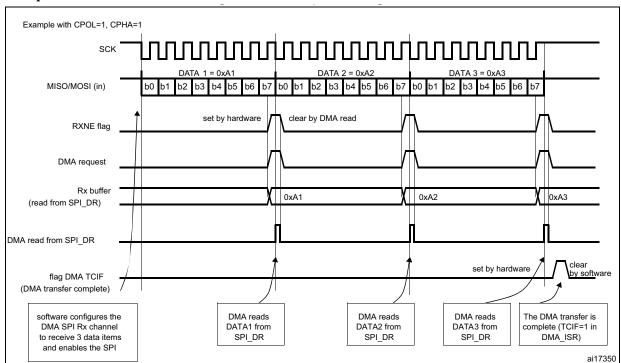

| 13. Контроллер ПДП (DMA)                                                                                                                                                                                                                    | 154                                                  |

| 13.1. Введение в DMA                                                                                                                                                                                                                        | 154                                                  |

| 13.2. Основные свойства DMA                                                                                                                                                                                                                 | 155                                                  |

| 13.3. Функциональное свойства DMA                                                                                                                                                                                                           | 156                                                  |

| 13.3.1. Транзакции DMA                                                                                                                                                                                                                      | 156                                                  |

| 13.3.2. Арбитр                                                                                                                                                                                                                              | 157                                                  |

| 13.3.3. Kаналы DMA                                                                                                                                                                                                                          | 157                                                  |

| 13.3.4. Ширина данных, выравнивание и порядок байт                                                                                                                                                                                          | 158                                                  |

| 13.3.5. Обработка ошибок                                                                                                                                                                                                                    | 159                                                  |

| 13.3.6. Прерывания                                                                                                                                                                                                                          | 159                                                  |

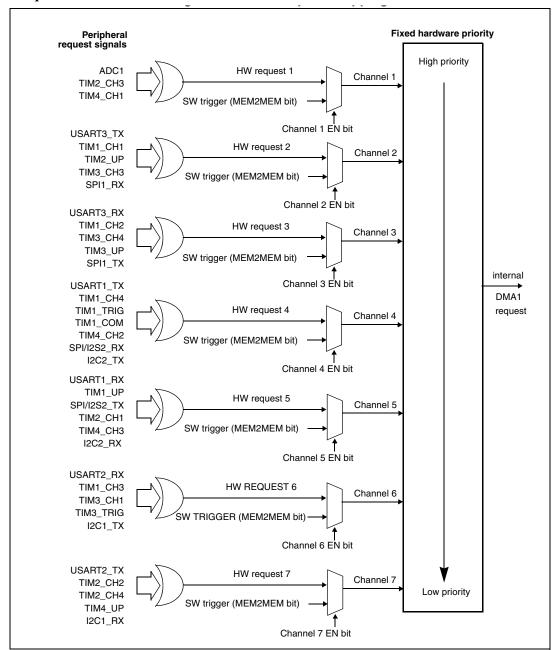

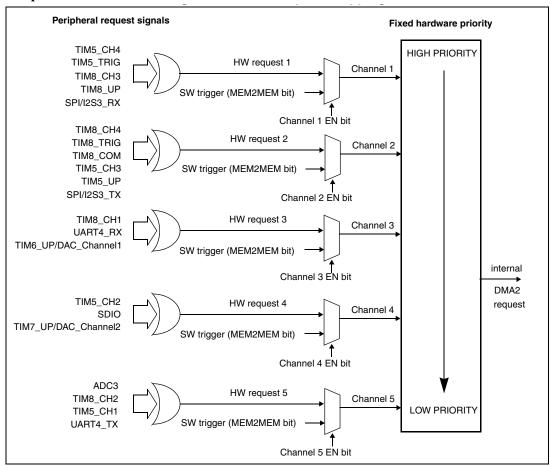

| 13.3.7. Распределение запросов DMA                                                                                                                                                                                                          | 159                                                  |

| 13.4. Регистры DMA                                                                                                                                                                                                                          | 162                                                  |

| 13.4.1. Регистр состояния прерываний (DMA_ISR)                                                                                                                                                                                              | 162                                                  |

| 13.4.2. Регистр очистки флагов прерываний (DMA_ISFR)                                                                                                                                                                                        | 162                                                  |

| 13.4.3. Регистр конфигурации канала х (DMA_CCRx) (x = 17)                                                                                                                                                                                   | 163                                                  |

| 13.4.4. Регистр числа данных канала х (DMA_CNDTRx) (x = 17)                                                                                                                                                                                 | 164                                                  |

| 13.4.5. Регистр адреса периферии канала х (DMA_CPARx) (х = 17)                                                                                                                                                                              | 164                                                  |

| 13.4.6. Регистр адреса памяти канала х (DMA_CPARx) (x = 17)                                                                                                                                                                                 | 165                                                  |

| 13.4.7. Карта регистров DMA                                                                                                                                                                                                                 |                                                      |

| ·                                                                                                                                                                                                                                           | ากอ                                                  |

| 4.4 V-v                                                                                                                                                                                                                                     | 165                                                  |

| ,                                                                                                                                                                                                                                           | 167                                                  |

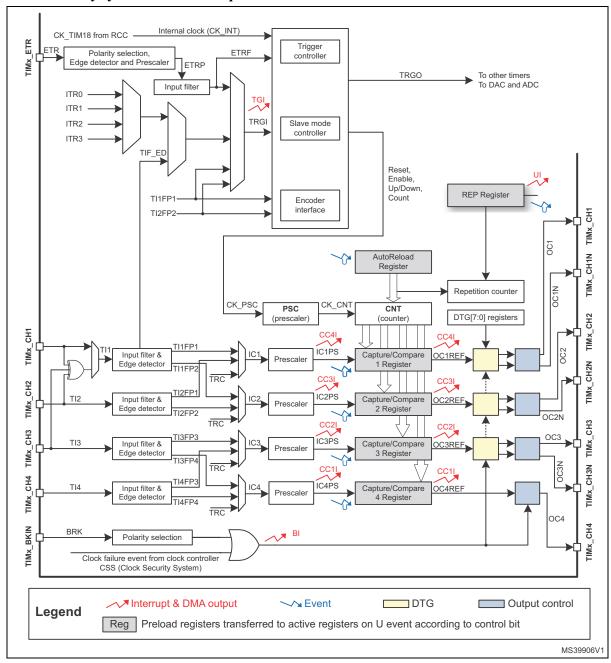

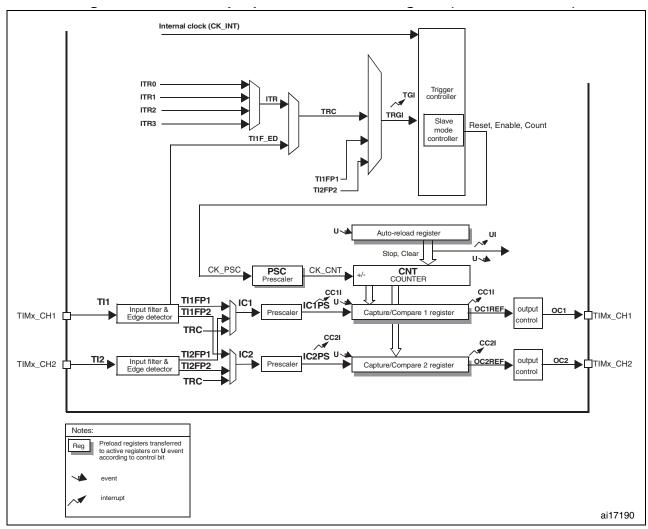

| 14.1. Введение в TIM1 и TIM8                                                                                                                                                                                                                | <b>167</b><br>167                                    |

| 14.1. Введение в ТІМ1 и ТІМ8<br>14.2. Основные свойства ТІМ1 и ТІМ8                                                                                                                                                                         | <b>167</b><br>167<br>167                             |

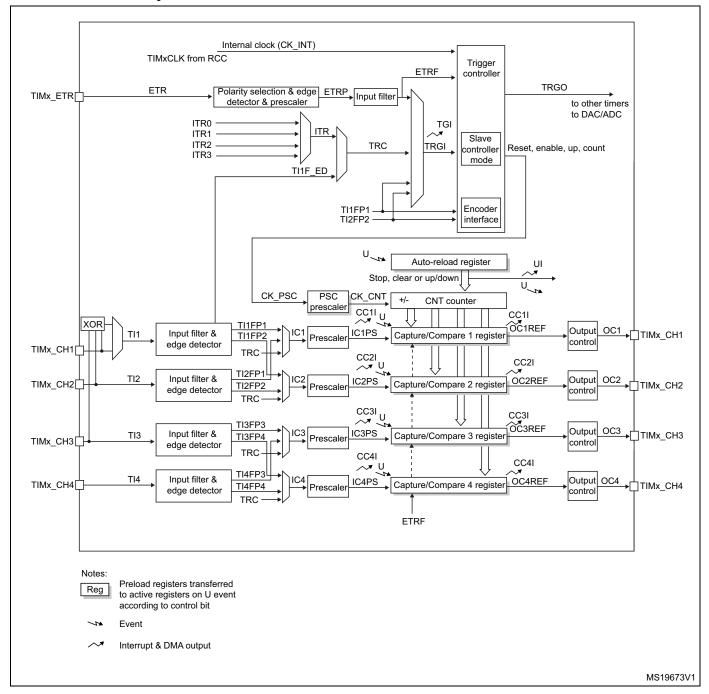

| 14.1. Введение в ТІМ1 и ТІМ8<br>14.2. Основные свойства ТІМ1 и ТІМ8<br>14.3. Функциональное описание таймеров                                                                                                                               | 167<br>167<br>167<br>168                             |

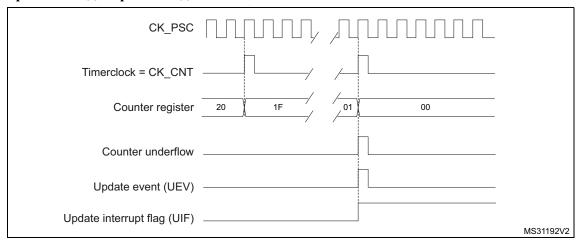

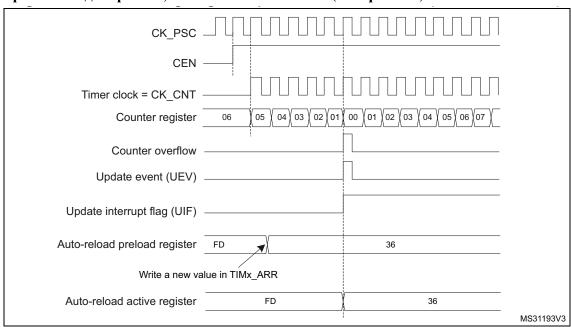

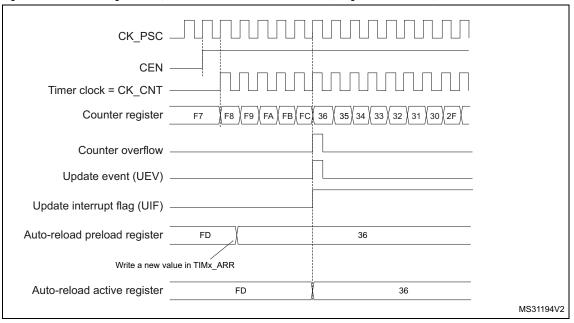

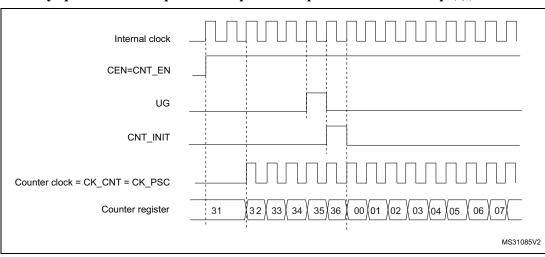

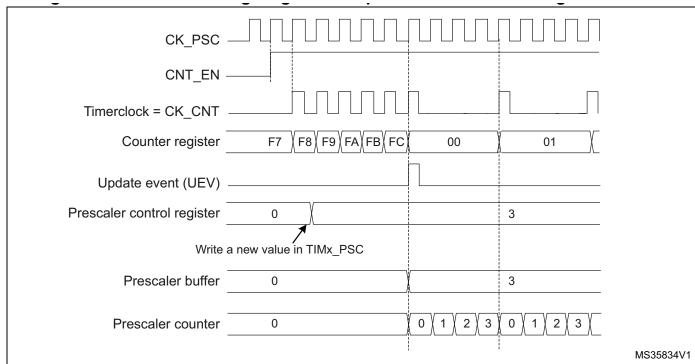

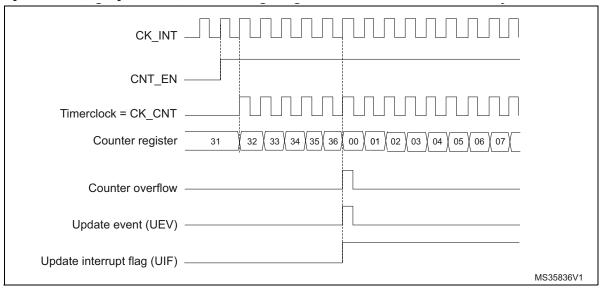

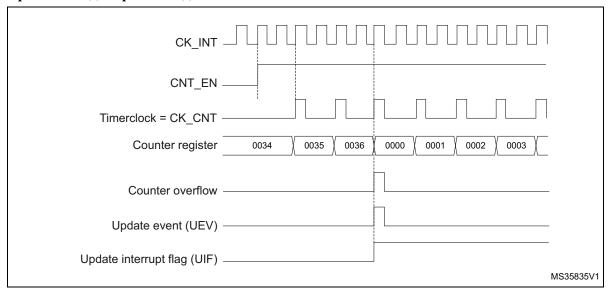

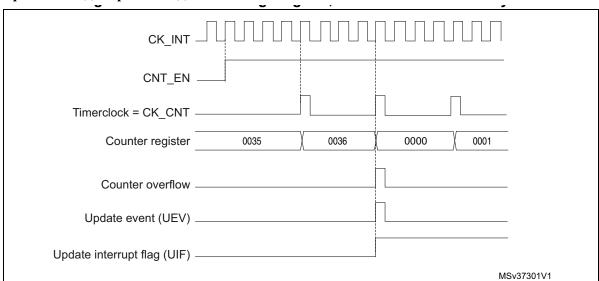

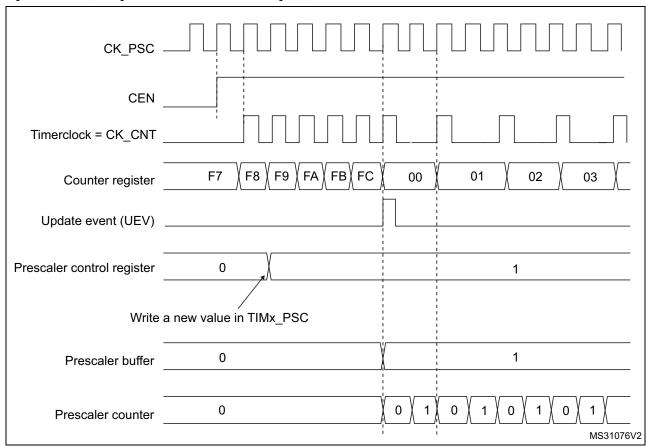

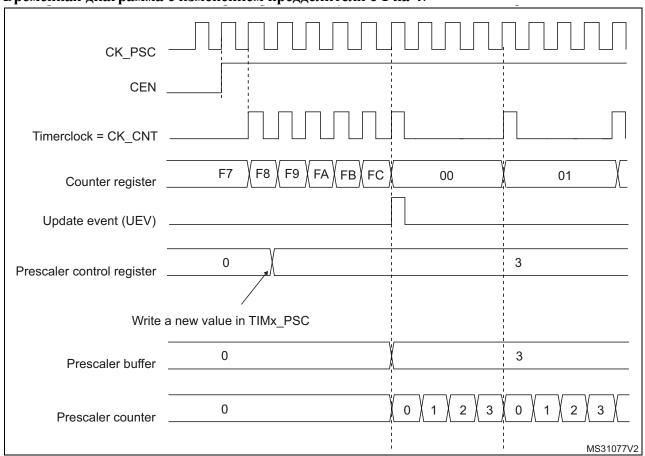

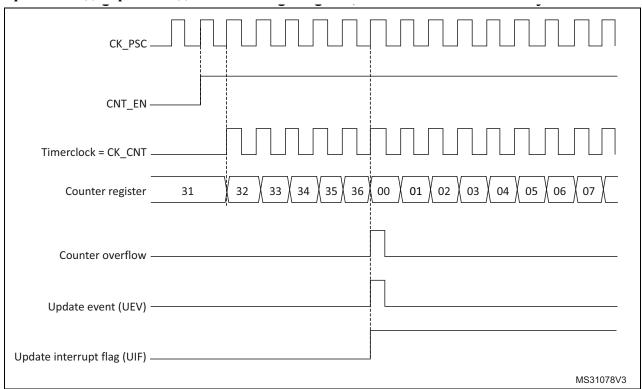

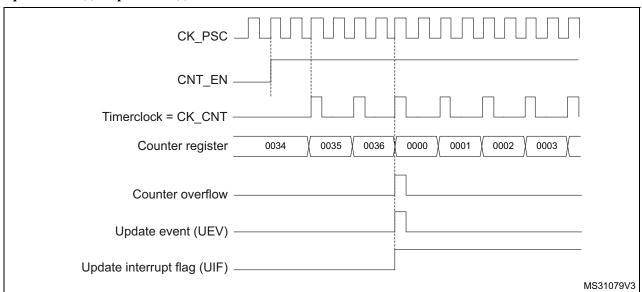

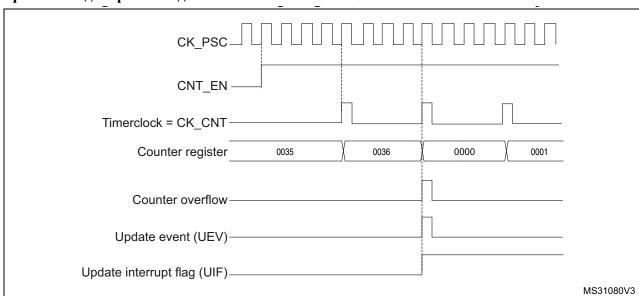

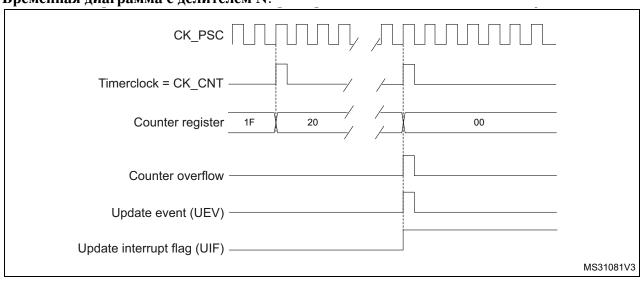

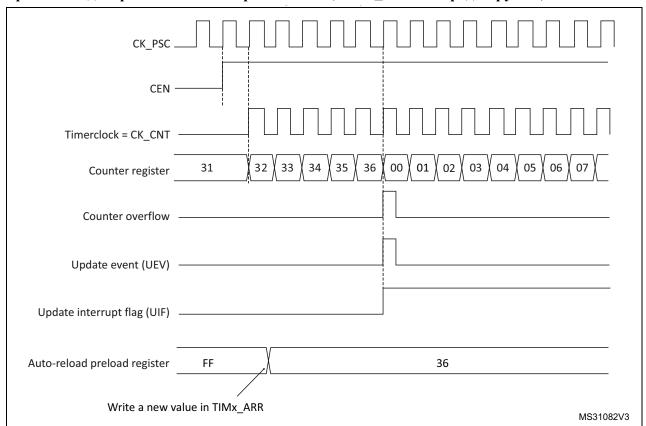

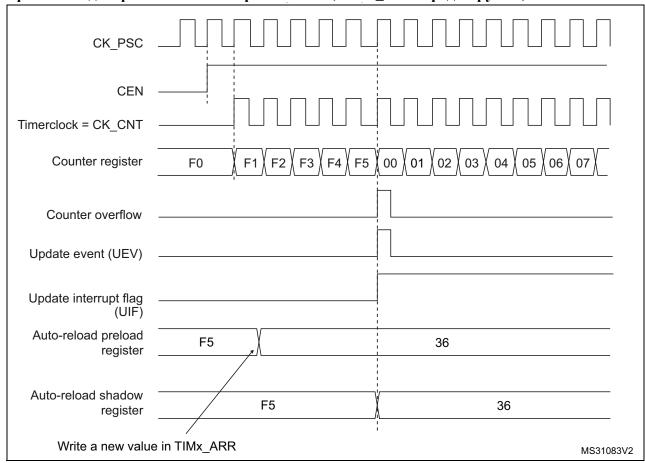

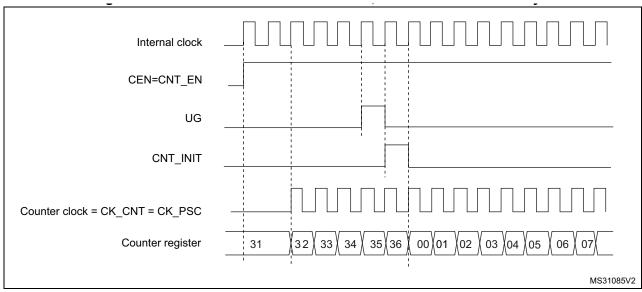

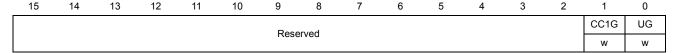

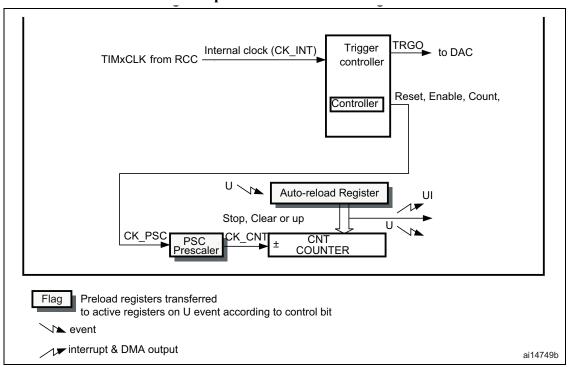

| <ul><li>14.1. Введение в ТІМ1 и ТІМ8</li><li>14.2. Основные свойства ТІМ1 и ТІМ8</li><li>14.3. Функциональное описание таймеров</li><li>14.3.1. Узел счёта</li></ul>                                                                        | 167<br>167<br>167<br>168<br>168                      |

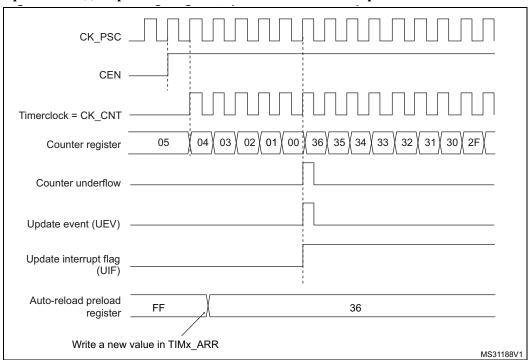

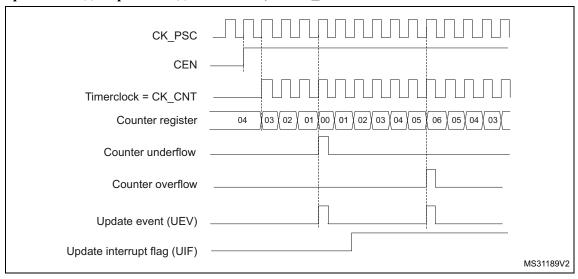

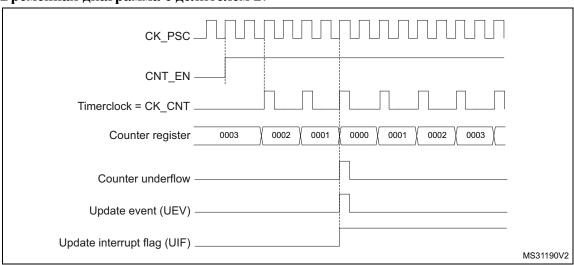

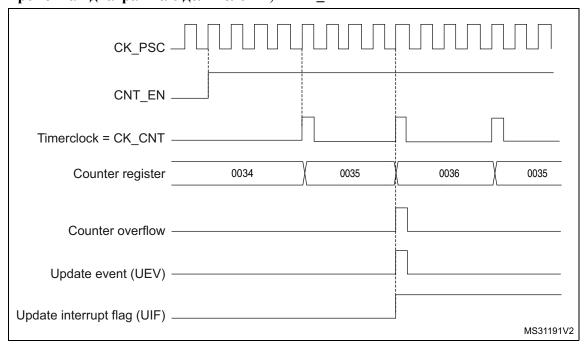

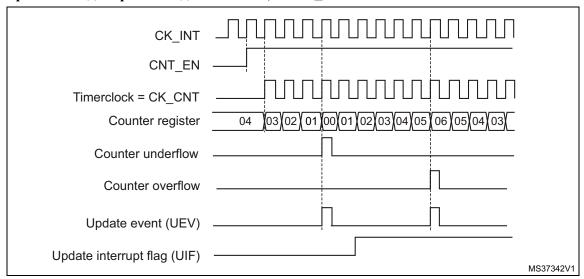

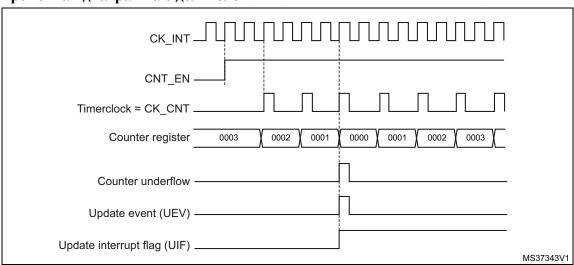

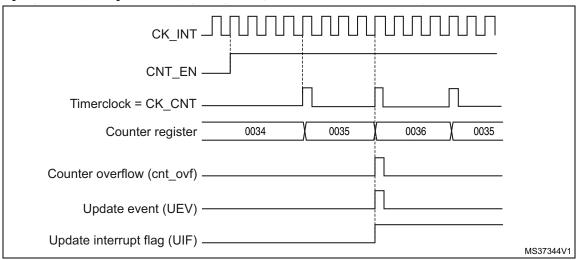

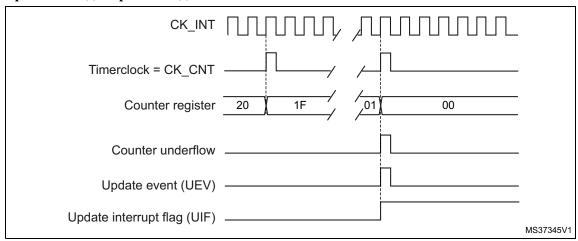

| <ul><li>14.1. Введение в ТІМ1 и ТІМ8</li><li>14.2. Основные свойства ТІМ1 и ТІМ8</li><li>14.3. Функциональное описание таймеров</li><li>14.3.1. Узел счёта</li><li>14.3.2. Режимы счёта</li></ul>                                           | 167<br>167<br>167<br>168<br>168<br>170               |

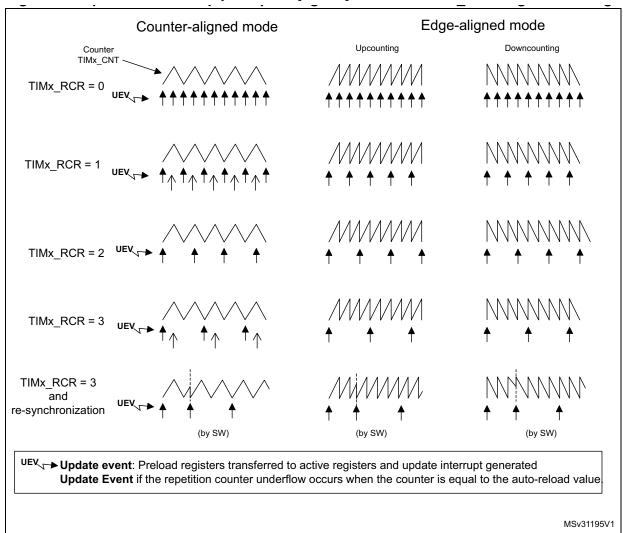

| <ul> <li>14.1. Введение в ТІМ1 и ТІМ8</li> <li>14.2. Основные свойства ТІМ1 и ТІМ8</li> <li>14.3. Функциональное описание таймеров</li> <li>14.3.1. Узел счёта</li> <li>14.3.2. Режимы счёта</li> <li>14.3.3. Счётчик повторения</li> </ul> | 167<br>167<br>167<br>168<br>168<br>170<br>178        |

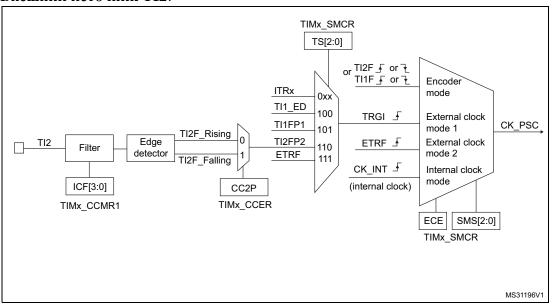

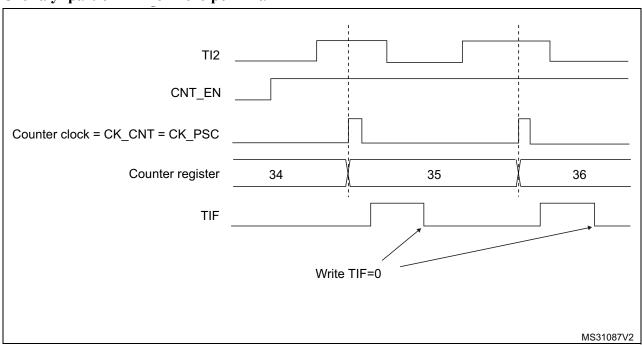

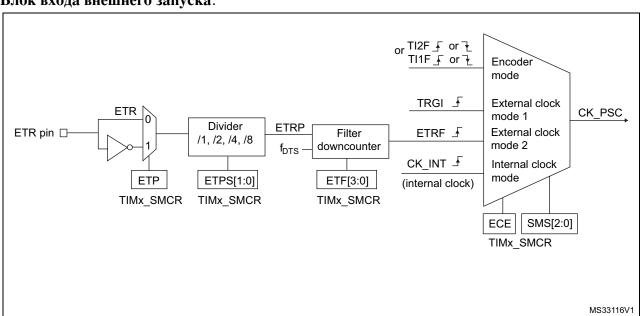

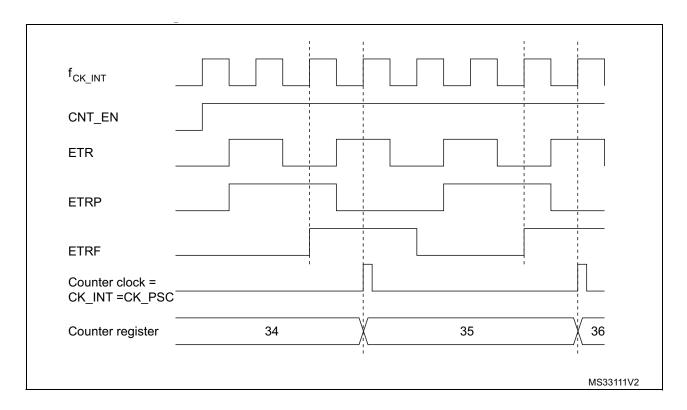

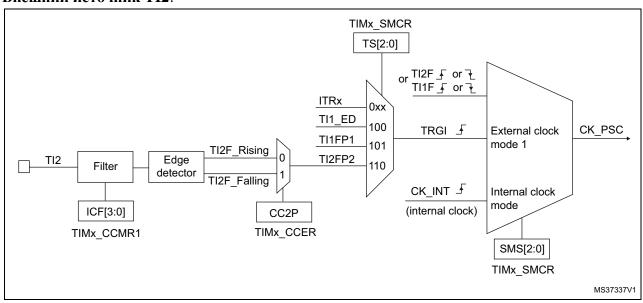

| 14.1. Введение в ТІМ1 и ТІМ8 14.2. Основные свойства ТІМ1 и ТІМ8 14.3. Функциональное описание таймеров 14.3.1. Узел счёта 14.3.2. Режимы счёта 14.3.3. Счётчик повторения 14.3.4. Выбор тактов                                             | 167<br>167<br>168<br>168<br>170<br>178<br>179        |

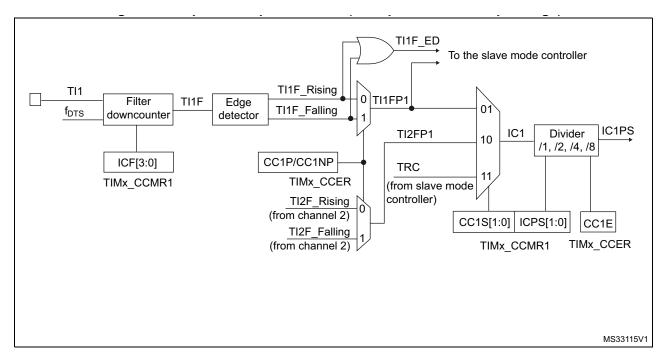

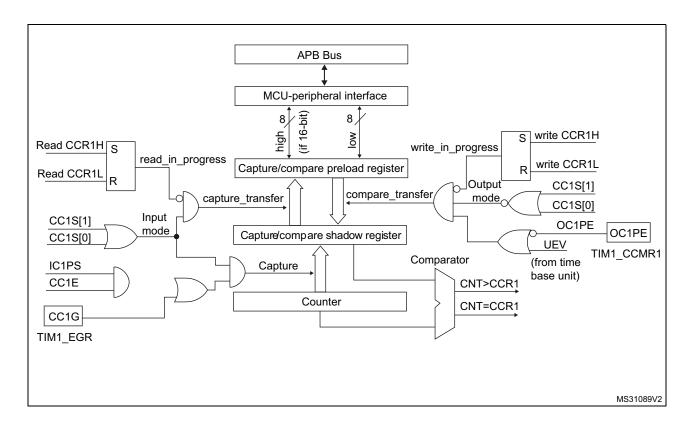

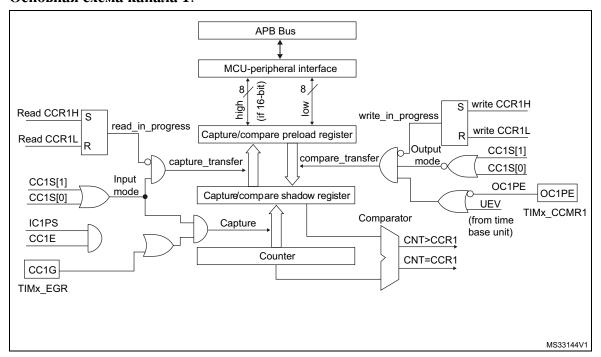

| 14.1. Введение в ТІМ1 и ТІМ8 14.2. Основные свойства ТІМ1 и ТІМ8 14.3. Функциональное описание таймеров 14.3.1. Узел счёта 14.3.2. Режимы счёта 14.3.3. Счётчик повторения 14.3.4. Выбор тактов 14.3.5. Каналы захвата/сравнения            | 167<br>167<br>168<br>168<br>170<br>178<br>179<br>181 |

| 14.1. Введение в ТІМ1 и ТІМ8 14.2. Основные свойства ТІМ1 и ТІМ8 14.3. Функциональное описание таймеров 14.3.1. Узел счёта 14.3.2. Режимы счёта 14.3.3. Счётчик повторения 14.3.4. Выбор тактов                                             | 167<br>167<br>168<br>168<br>170<br>178<br>179        |

| 14.3.8. Принудительный вывод                                | 185 |

|-------------------------------------------------------------|-----|

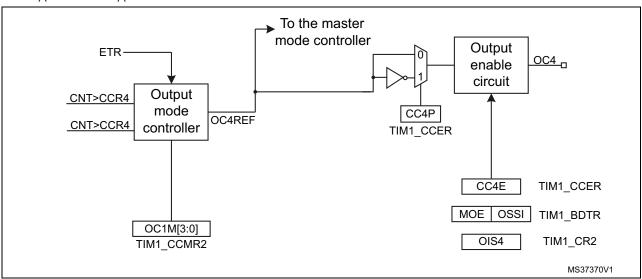

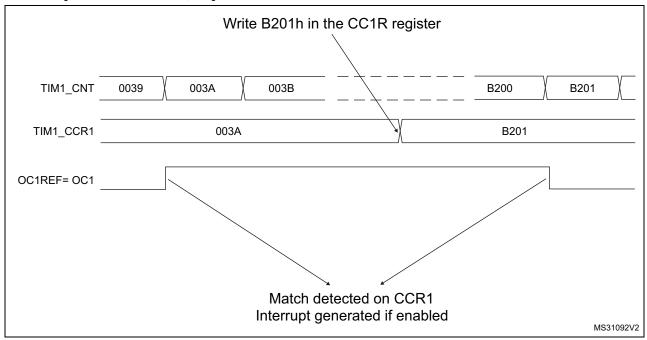

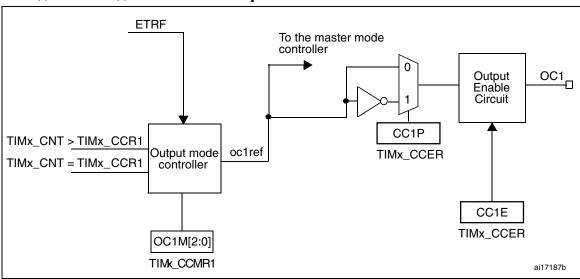

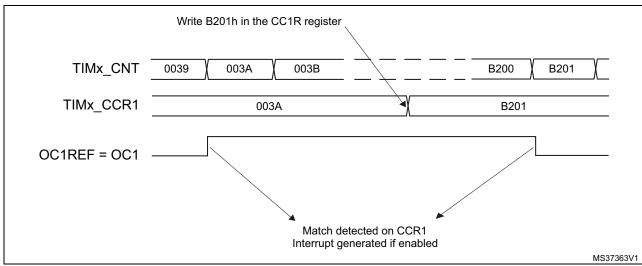

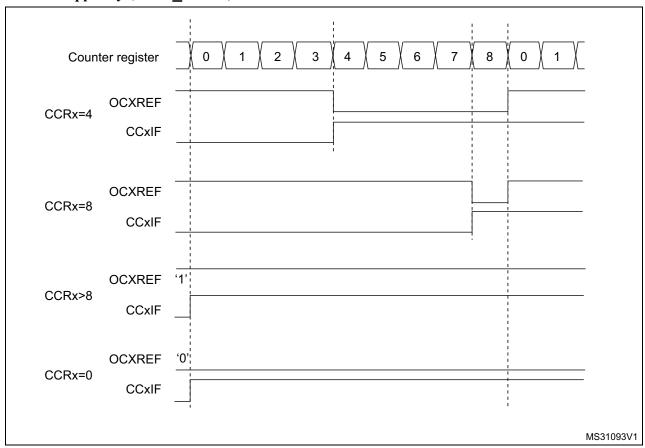

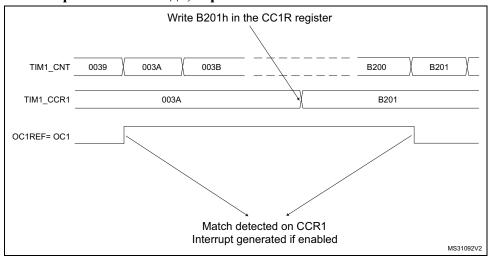

| 14.3.9. Режим сравнения выхода                              | 185 |

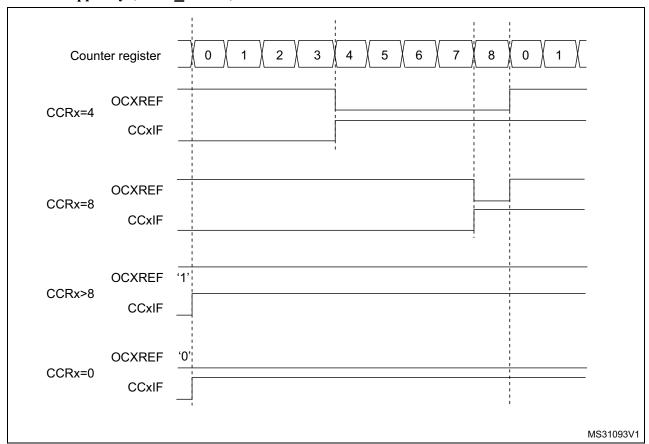

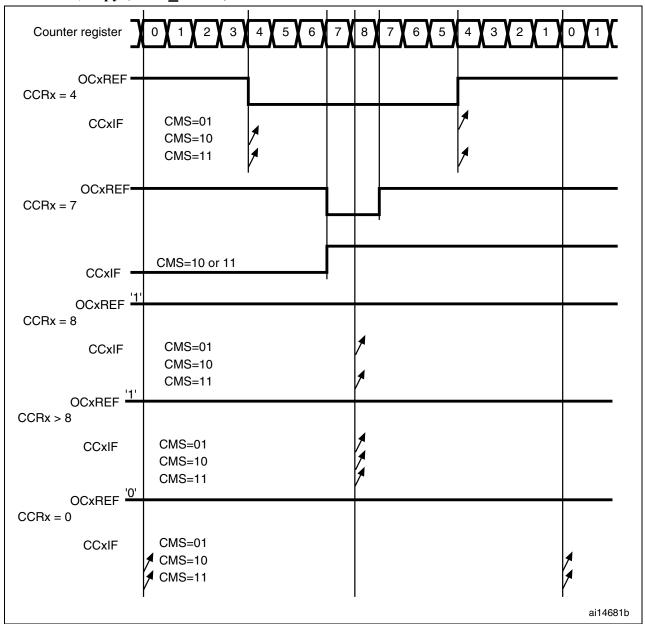

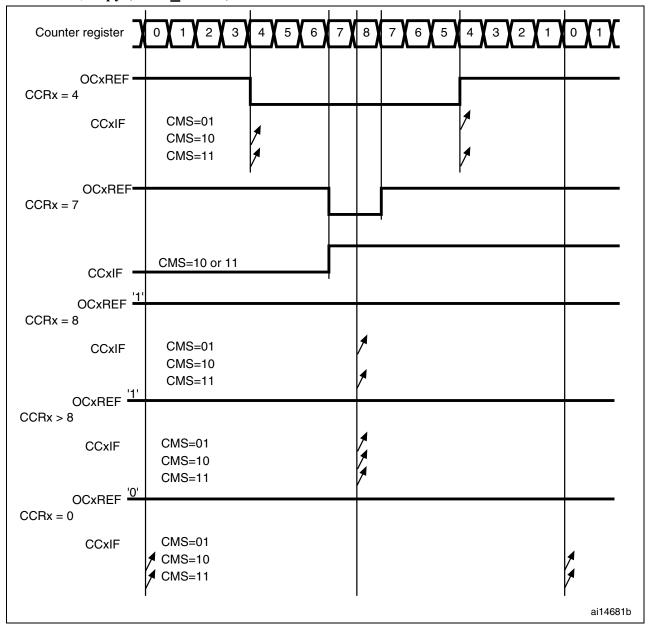

| 14.3.10.Режим ШИМ                                           | 186 |

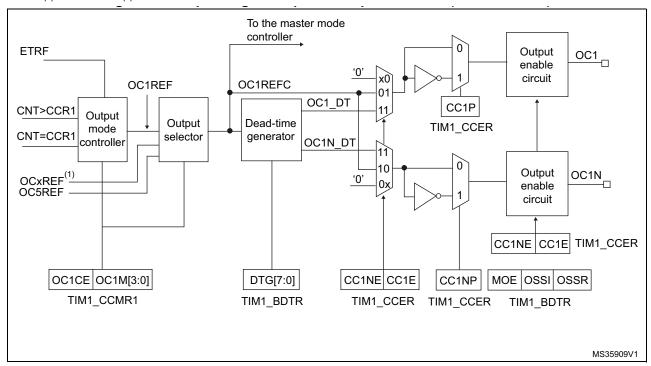

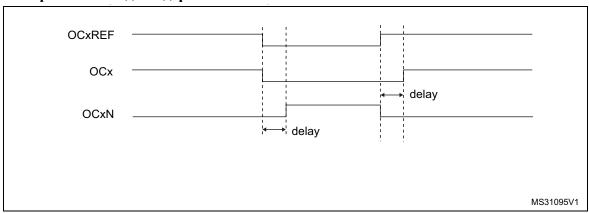

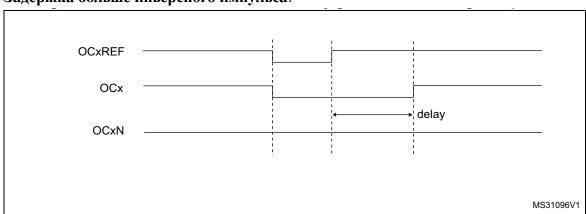

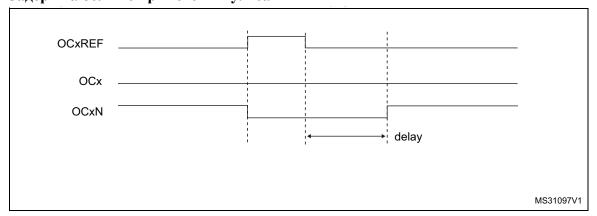

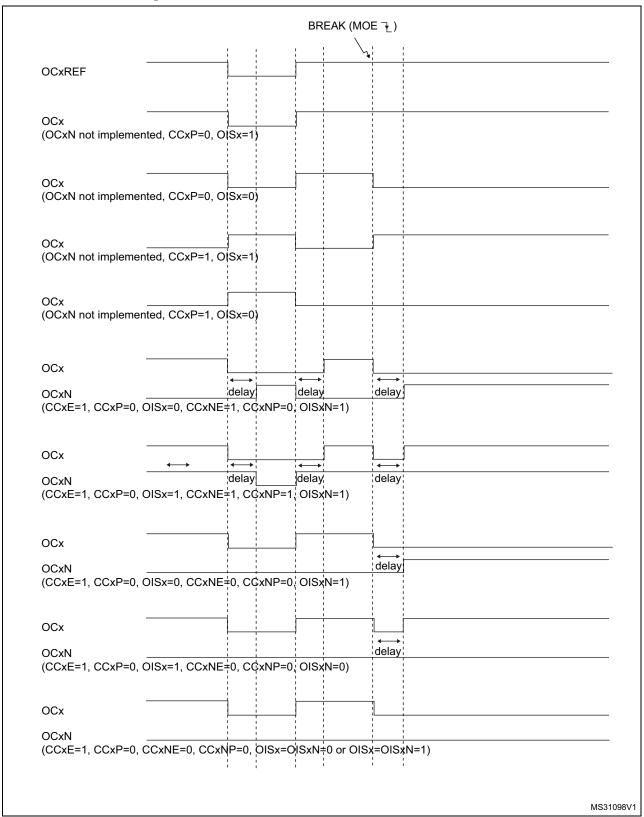

| 14.3.11.Инверсные выходы и задержка                         | 188 |

| 14.3.12.Функция останова                                    | 190 |

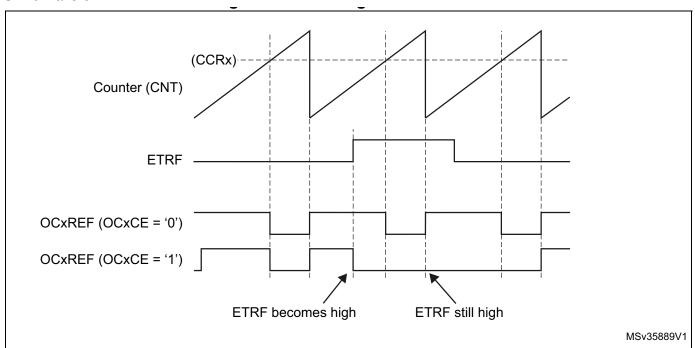

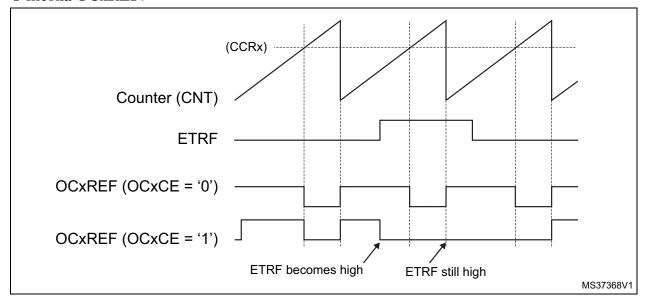

| 14.3.13.Очистка OCxREF по внешнему событию                  | 192 |

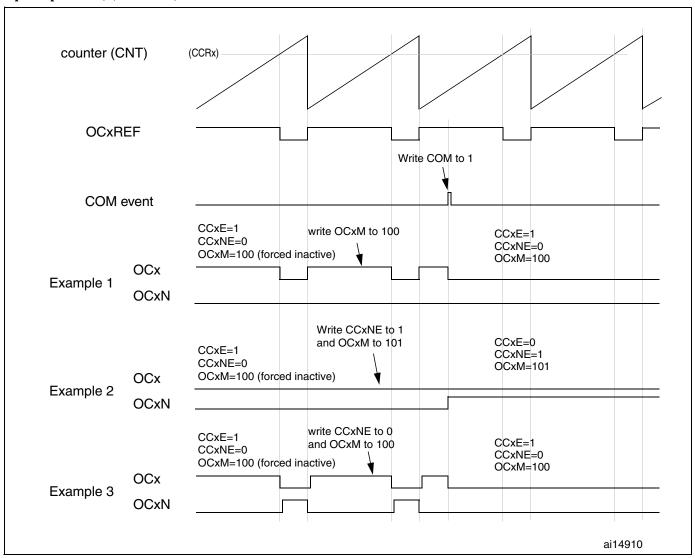

| 14.3.14.Шести-шаговая ШИМ                                   | 192 |

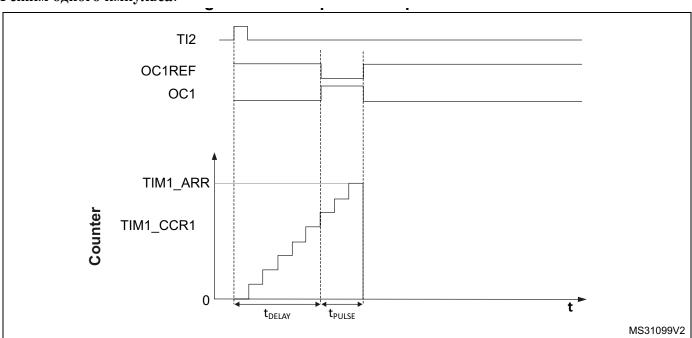

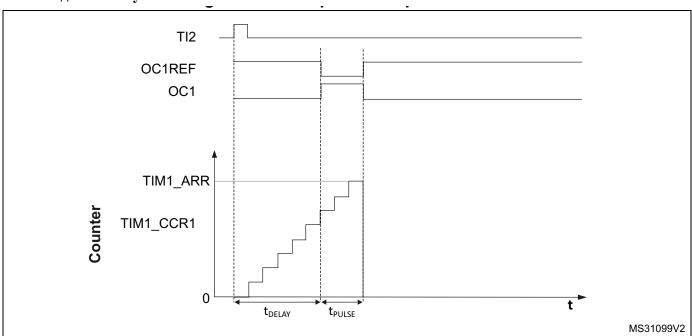

| 14.3.15.Режим одного импульса                               | 193 |

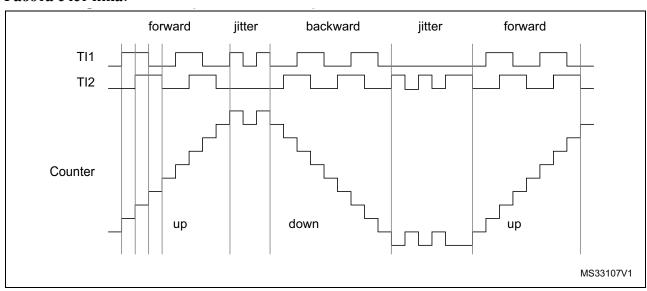

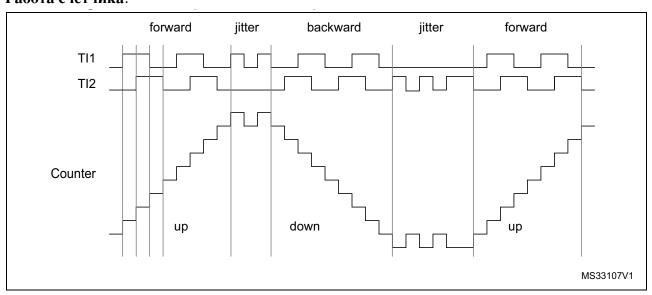

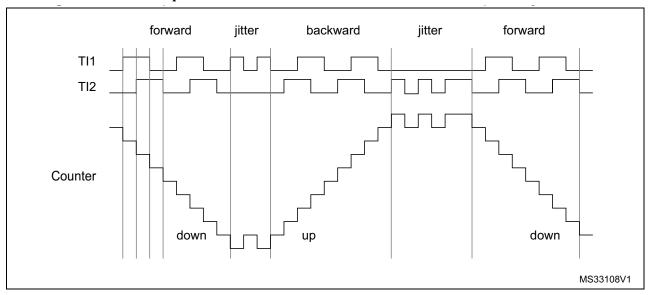

| 14.3.16.Режим интерфейса кодера                             | 195 |

| 14.3.17.Функция XOR входов таймера                          | 196 |

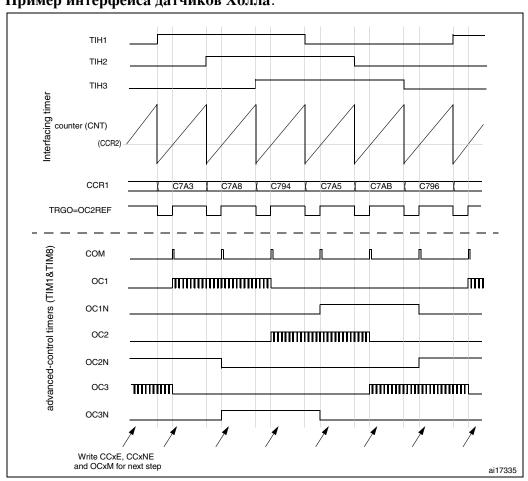

| 14.3.18.Работа с датчиками Холла                            | 196 |

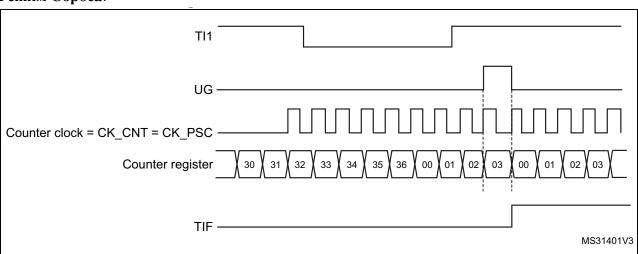

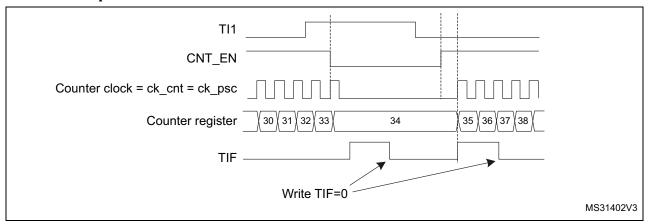

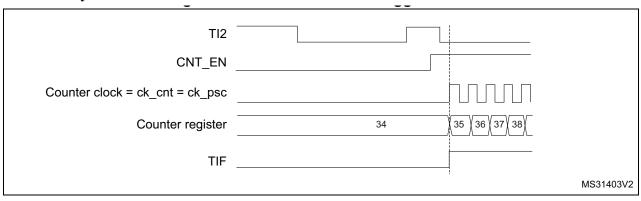

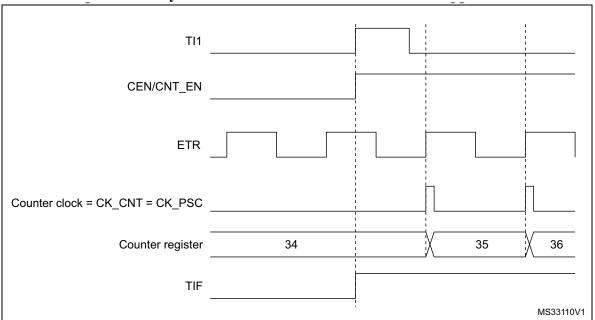

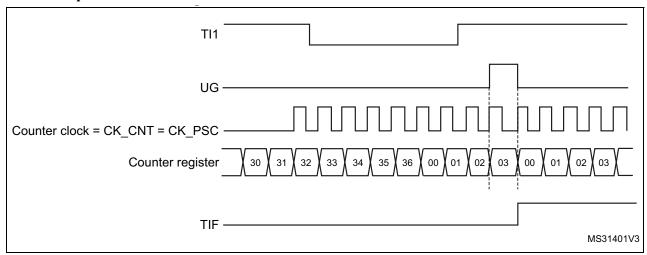

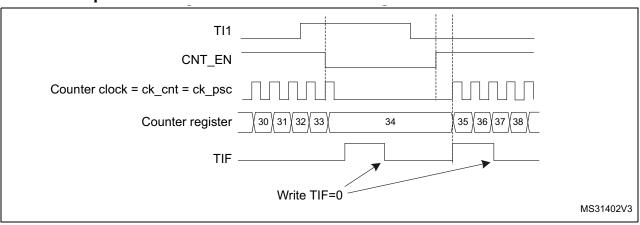

| 14.3.19.TIMх и синхронизация внешнего запуска               | 198 |

| 14.3.20.Синхронизация таймера                               | 200 |

| 14.3.21.Режим отладки                                       | 200 |

| 14.4. Регистры ТІМ1 и ТІМ8                                  | 200 |

| 14.4.1. Регистр управления 1 (TIMx_CR1)                     | 200 |

| 14.4.2. Регистр управления 2 (TIMx_CR2)                     | 201 |

| 14.4.3. Регистр управления режима ведомого (TIMx_SMCR)      | 202 |

| 14.4.4. Регистр разрешения прерываний/DMA (TIMx_DIER)       | 204 |

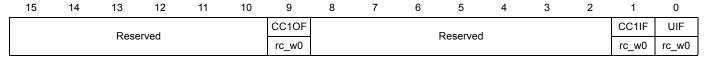

| 14.4.5. Регистр состояния (TIMx_SR)                         | 204 |

| 14.4.6. Регистр генерации событий (TIMx_EGR)                | 205 |

| 14.4.7. Регистр режима захвата/сравнения 1 (TIMx_CCMR1)     | 206 |

| 14.4.8. Регистр режима захвата/сравнения 2 (TIMx_CCMR2)     | 208 |

| 14.4.9. Регистр разрешения захвата/сравнения (TIMx_CCER)    | 209 |

| 14.4.10.Счётчик TIM1 и TIM8 (TIMx_CNT)                      | 211 |

| 14.4.11.Предделитель TIM1 и TIM8 (TIMx_PSC)                 | 211 |

| 14.4.12.Регистр предзагрузки TIM1 и TIM8 (TIMx_ARR)         | 211 |

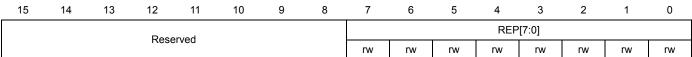

| 14.4.13.Счётчик повторения ТІМ1 и ТІМ8 (TІМх_RCR)           | 211 |

| 14.4.14.Регистр 1 захвата/сравнения TIM1 и TIM8 (TIMx_CCR1) | 212 |

| 14.4.15.Регистр 2 захвата/сравнения ТІМ1 и ТІМ8 (ТІМх_ССR2) | 212 |

| 14.4.16.Регистр 3 захвата/сравнения ТІМ1 и ТІМ8 (ТІМх_ССR3) | 212 |

| 14.4.17.Регистр 4 захвата/сравнения TIM1 и TIM8 (TIMx_CCR4) | 213 |

| 14.4.18.Регистр останова и задержки (TIMx_BDTR )            | 213 |

| 14.4.19.Регистр управления DMA TIM1 и TIM8 (TIMx_DCR)       | 214 |

| 14.4.20.Регистр адреса полного доступа DMA (TIMx_DMAR)      | 215 |

| 14.4.21.Карта регистров ТІМ1 и ТІМ8                         | 216 |

| 15. Таймеры общего назначения (TIM2 - TIM5)                 | 217 |

| 15.1. Введение в TIM2 - TIM5                                | 217 |

| 15.2. Основные свойства TIM2 - TIM5                         | 217 |

| 15.3. Функциональное описание таймеров TIM2 - TIM5          | 218 |

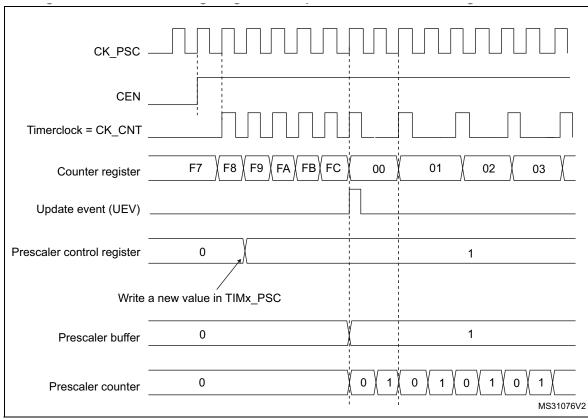

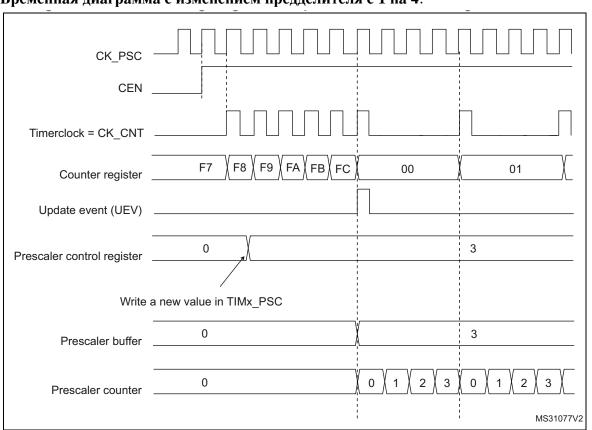

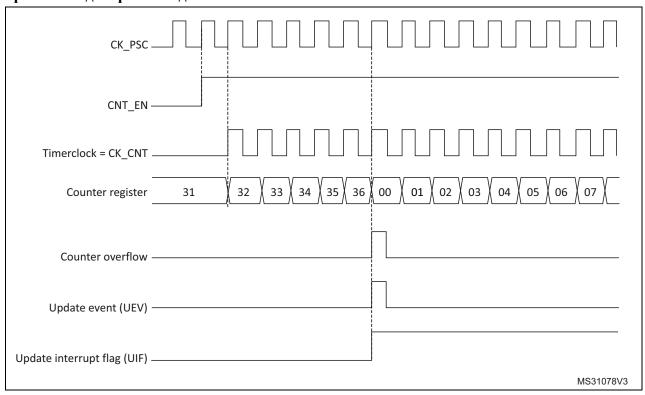

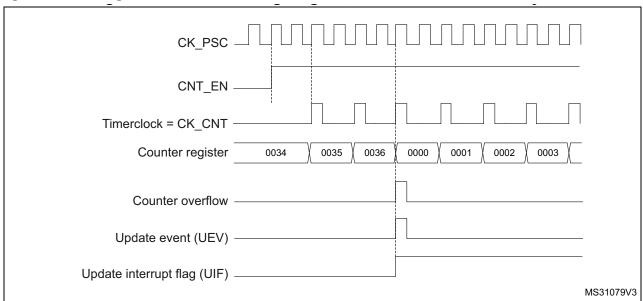

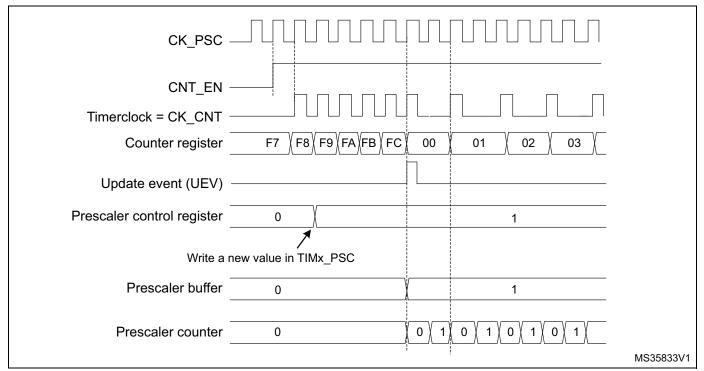

| 15.3.1. Узел счёта                                          | 218 |

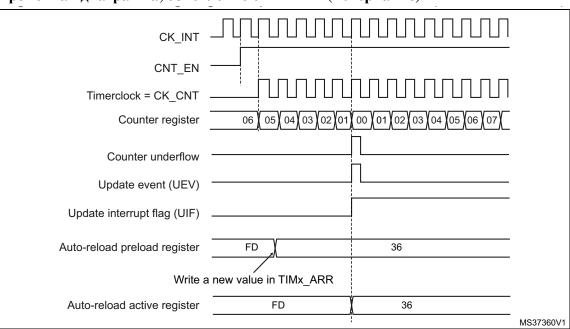

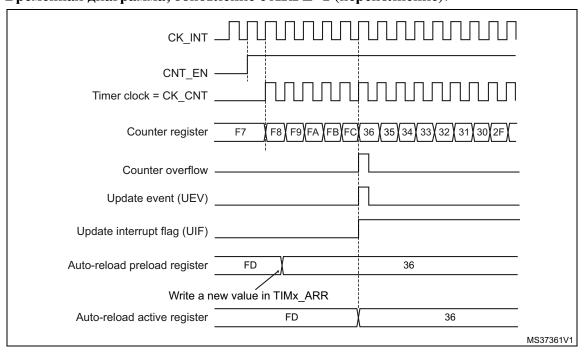

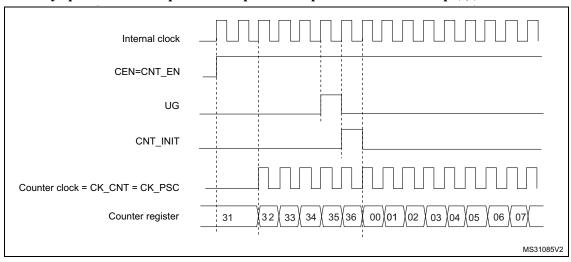

| 15.3.2. Режимы счёта                                        | 220 |

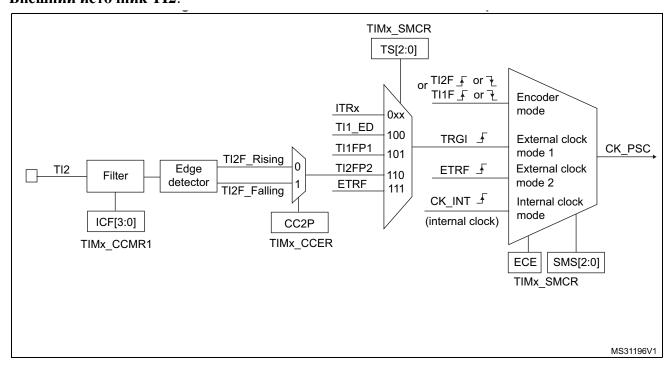

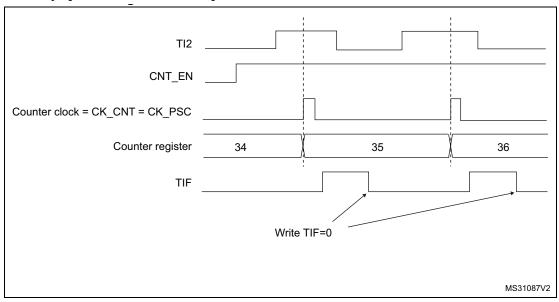

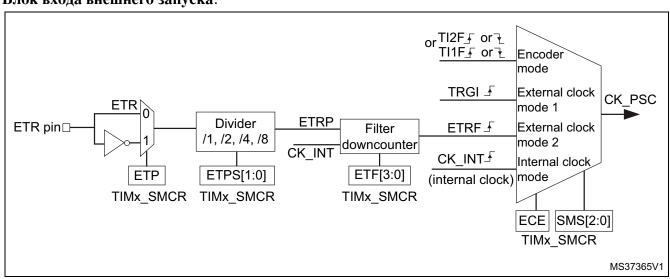

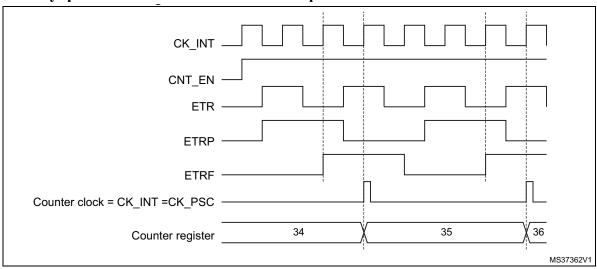

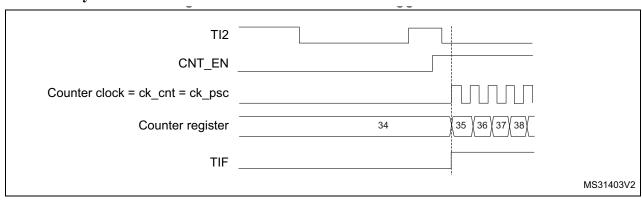

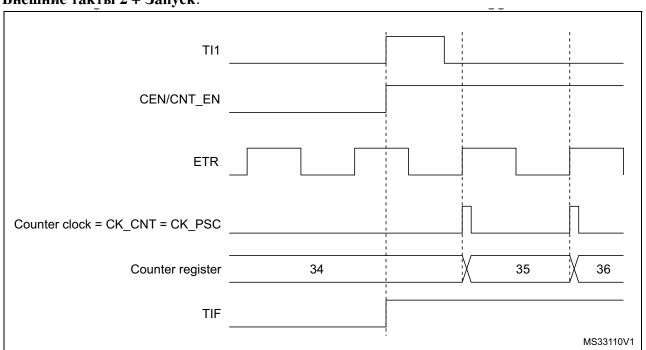

| 15.3.3. Выбор тактов                                        | 227 |

| 15.3.4. Каналы захвата/сравнения                            | 229 |

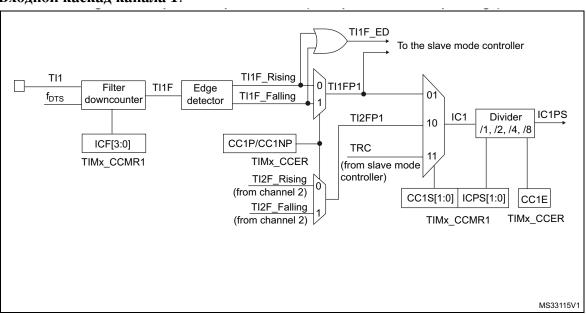

| 15.3.5. Режим захвата входа                                 | 230 |

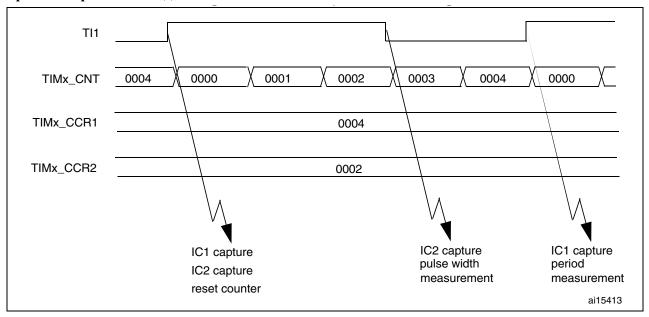

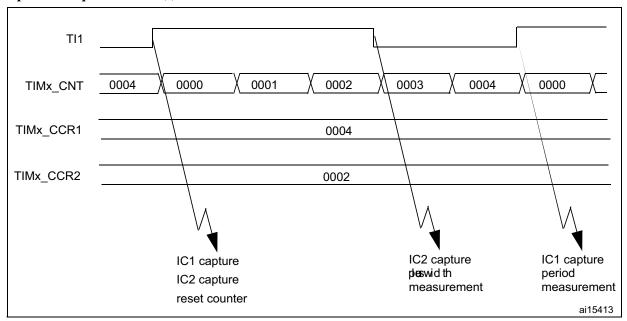

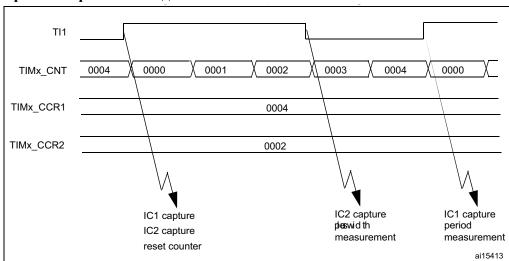

| 15.3.6. Режим ввода ШИМ                                     | 231 |

| 15.3.7. Принудительный вывод                                | 232 |

| 15.3.8. Режим сравнения выхода                              | 232 |

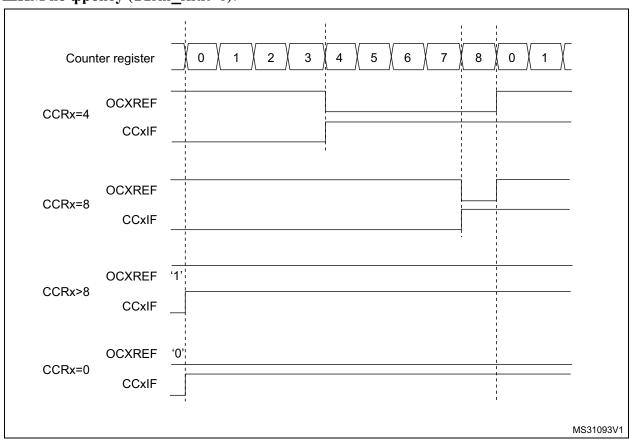

| 15.3.9. Режим ШИМ                                           | 233 |

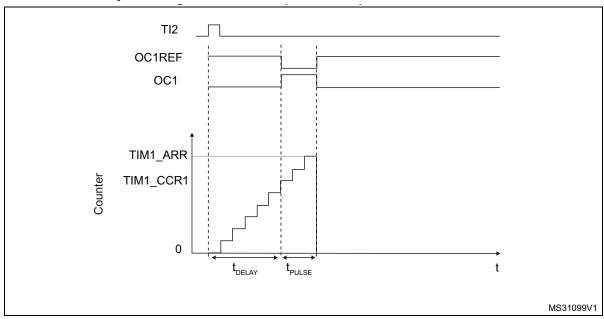

| 15.3.10.Режим одного импульса (OPM)                         | 235 |

| 15.3.11.Очистка OCxREF по внешнему событию                  | 237 |

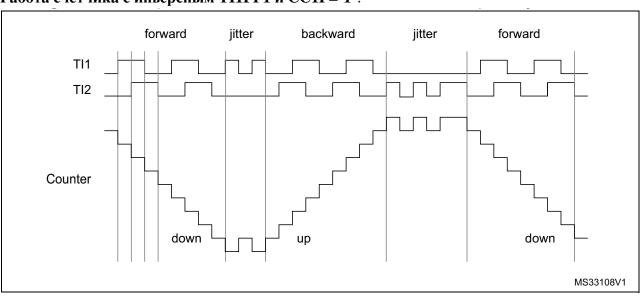

| 15.3.12.Режим интерфейса кодера                             | 237 |

| 15.3.13.Функция XOR входов таймера                          | 239 |

| 15.3.14.Синхронизация внешнего запуска TIMx                 | 239 |

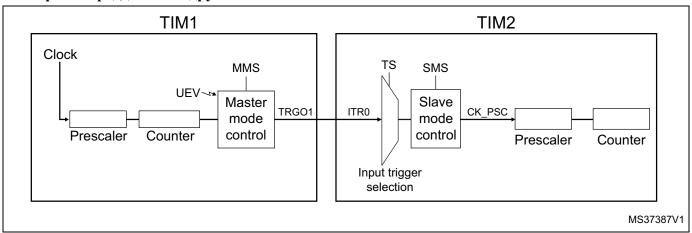

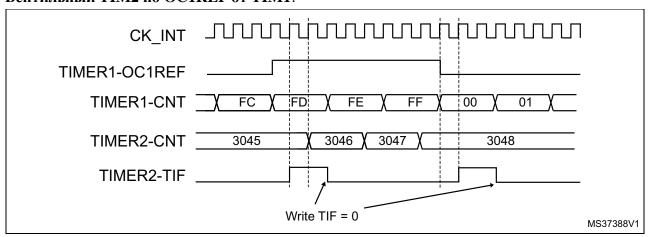

| 15.3.15.Синхронизация таймера                               | 242 |

| 15.3.16.Режим отладки                                       | 245 |

| 15.4. Регистры TIMx                                         | 246 |

| 15.4.1. Регистр управления 1 (TIMx_CR1)                     | 246 |

| 15.4.2. Регистр управления 2 (TIMx_CR2)                     | 247 |

| 15.4.3. Регистр управления режима ведомого (TIMx_SMCR)                                | 247 |

|---------------------------------------------------------------------------------------|-----|

| 15.4.4. Регистр разрешения прерываний/DMA (TIMx_DIER)                                 | 249 |

| 15.4.5. Регистр состояния (TIMx_SR)                                                   | 249 |

| 15.4.6. Регистр генерации событий (TIMx_EGR)                                          | 250 |

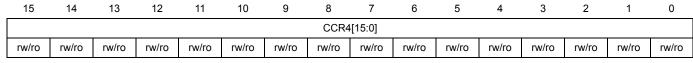

| 15.4.7. Регистр режима захвата/сравнения 1 (TIMx_CCMR1)                               | 251 |

| 15.4.8. Регистр режима захвата/сравнения 2 (TIMx_CCMR2)                               | 253 |

| 15.4.9. Регистр разрешения захвата/сравнения (TIMx_CCER)                              | 254 |

| 15.4.10.Счётчик TIM2 - TIM5 (TIMx_CNT)                                                | 255 |

| 15.4.11.Предделитель TIM2 - TIM5 (TIMx_PSC)                                           | 255 |

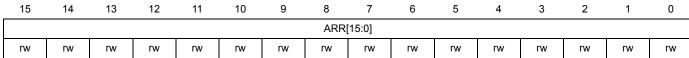

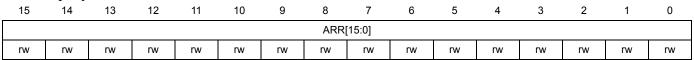

| 15.4.12.Регистр предзагрузки TIM2 - TIM5 (TIMx_ARR)                                   | 255 |

| 15.4.13.Регистр 1 захвата/сравнения TIM2 - TIM5 (TIMx_CCR1)                           | 255 |

| 15.4.14.Регистр 2 захвата/сравнения TIM2 - TIM5 (TIMx_CCR2)                           | 256 |

| 15.4.15.Регистр 3 захвата/сравнения TIM2 - TIM5 (TIMx_CCR3)                           | 256 |

| 15.4.16.Регистр 4 захвата/сравнения TIM2 - TIM5 (TIMx_CCR4)                           | 256 |

| 15.4.17.Регистр управления DMA (TIMx_DCR)                                             | 257 |

| 15.4.18.Регистр адреса полного доступа DMA (TIMx_DMAR)                                | 257 |

| 15.4.19.Карта регистров ТІМ2 - ТІМ5                                                   | 258 |

|                                                                                       |     |

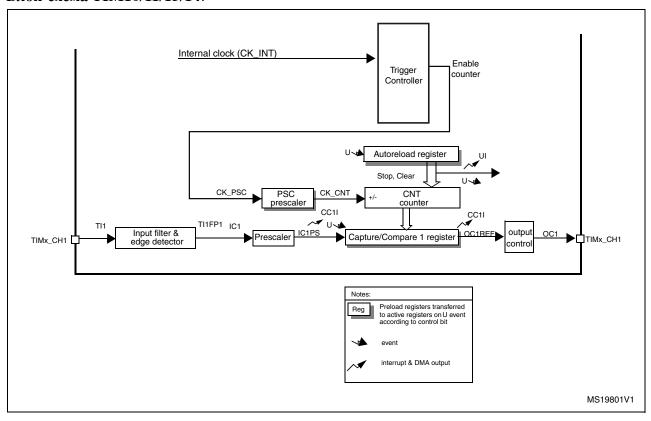

| 16. Таймеры общего назначения (TIM9 - TIM14)                                          | 259 |

| 16.1. Введение в TIM9 - TIM14                                                         | 259 |

| 16.2. Основные свойства TIM9 - TIM14                                                  | 259 |

| 16.2.1. Основные свойства TIM9/TIM12                                                  | 259 |

| 16.2.2. Основные свойства ТІМ10/ТІМ11 и ТІМ13/ТІМ14                                   | 260 |

| 16.3. Функциональное описание таймеров TIM9 - TIM14                                   | 261 |

| 16.3.1. Узел счёта                                                                    | 261 |

| 16.3.2. Режимы счёта                                                                  | 263 |

| 16.3.3. Выбор тактов                                                                  | 266 |

| 16.3.4. Каналы захвата/сравнения                                                      | 267 |

| 16.3.5. Режим захвата входа                                                           | 268 |

| 16.3.6. Режим ввода ШИМ (только TIM9/TIM12)                                           | 269 |

| 16.3.7. Принудительный вывод                                                          | 270 |

| 16.3.8. Режим сравнения выхода                                                        | 270 |

| 16.3.9. Режим ШИМ                                                                     | 271 |

| 16.3.10.Режим одного импульса (ОРМ)                                                   | 271 |

| 16.3.11.Синхронизация внешнего запуска ТІМ9/12                                        | 273 |

| 16.3.12.Синхронизация таймера TIM9/TIM12                                              | 274 |

| 16.3.13.Режим отладки                                                                 | 275 |

| 16.4. Регистры ТІМ9/12                                                                | 275 |

| 16.4.1. Регистр управления 1 TIM9/12 (TIMx_CR1)                                       | 275 |

| 16.4.2. Регистр управления режима ведомого TIM9/12 (TIMx_SMCR)                        | 276 |

| 16.4.3. Регистр разрешения прерываний TIM9/TIM12 (TIMx_DIER)                          | 276 |

| 16.4.4. Регистр разрешения ТІМ9/ТІМ12 (ТІМх_SR)                                       | 277 |

| 16.4.5. Регистр генерации событий (TIMx_EGR)                                          | 277 |

| 16.4.6. Регистр режима захвата/сравнения 1 TIM9/TIM12 (TIMx_CCMR1)                    | 278 |

| 16.4.7. Регистр разрешения захвата/сравнения (TIMx_CCER)                              | 280 |

| 16.4.8. Счётчик ТІМ9/12 (ТІМх_СNТ)                                                    | 281 |

| 16.4.9. Предделитель TIM9/12 (TIMx_PSC)                                               | 281 |

| 16.4.10.Регистр предзагрузки TIM9/12 (TIMx_ARR)                                       | 281 |

| 16.4.11.Регистр 1 захвата/сравнения TIM9/12 (TIMx_CCR1)                               | 281 |

| 16.4.12.Регистр 2 захвата/сравнения TIM9/12 (TIMx_CCR2)                               | 282 |

| 16.4.13.Карта регистров ТІМ9/12                                                       | 283 |

| · · ·                                                                                 |     |

| 16.5. Регистры TIM10/11/13/14 16.5.1. Регистр управления 1 TIM10/11/13/14 (TIMX, CP1) | 283 |

| 16.5.1. Регистр управления 1 TIM10/11/13/14 (TIMx_CR1)                                | 283 |

| 16.5.2. Регистр разрешения прерываний TIM10/11/13/14 (TIMx_DIER)                      | 284 |

| 16.5.3. Регистр состояния TIM10/11/13/14 (TIMx_SR)                                    | 285 |

| 16.5.4. Регистр генерации событий TIM10/11/13/14 (TIMx_EGR)                           | 285 |

| 16.5.5. Регистр режима захвата/сравнения TIM10/11/13/14 (TIMx_CCMR1)                  | 285 |

| 16.5.6. Разрешение захвата/сравнения TIM10/11/13/14 (TIMx_CCER)                       | 287 |

| 16.5.7. Счётчик TIM10/11/13/14 (TIMx_CNT)                                             | 288 |

| 16.5.8. Предделитель TIM10/11/13/14 (TIMx_PSC)                                        | 288 |

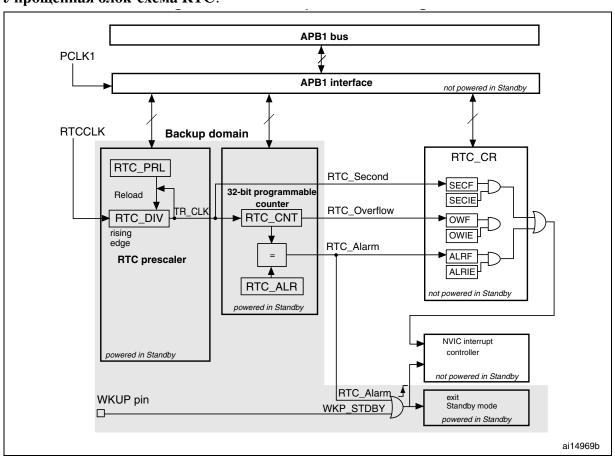

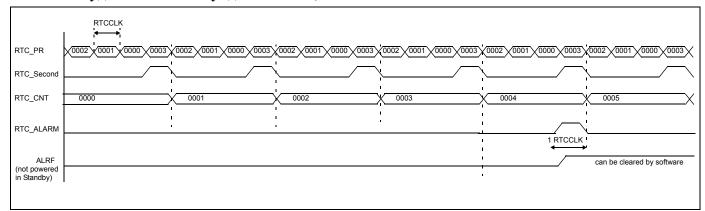

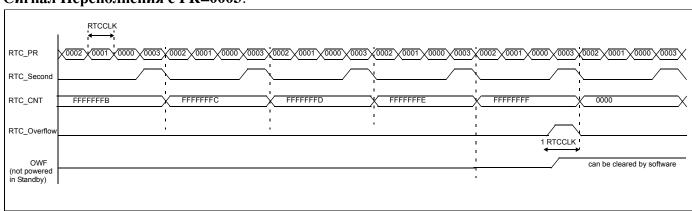

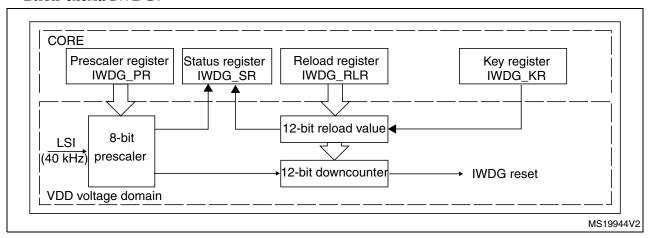

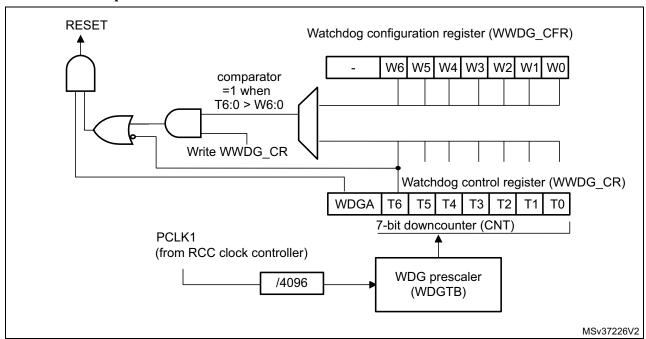

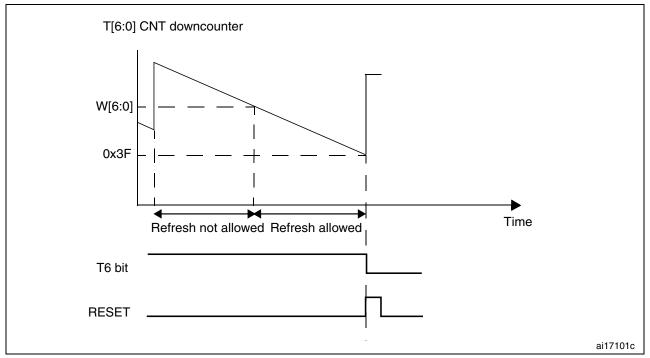

| 18.4.5. Регистры счётчика RTC (RTC_CNTH / RTC_CNTL) 18.4.6. Регистры будильника RTC (RTC_ALRH / RTC_ALRL) 303 18.5. Карта регистров RTC 304 19. Независимый сторожевой таймер (IWDG) 304 19.1. Введение в IWDG 19.2. Основные свойства IWDG 19.3. Функциональное описание IWDG 19.3.1. Аппаратный сторож 305                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16.5.9. Регистр предзагрузки TIM10/11/13/14 (TIMx_ARR) 16.5.10.Регистр 1 захвата/сравнения TIM10/11/13/14 (TIMx_CCR1) | 288<br>288 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------|

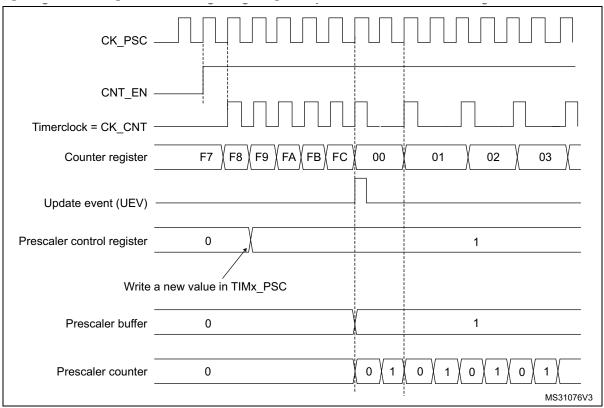

| 17.1. Введение в ТІМ6 и ТІМ7  17.2. Основные свойства ТІМ6 и ТІМ7  17.3. Оункциональное описание таймеров ТІМ6 и ТІМ7  290  17.3.1. Узал счёта  292  17.3.2. Режим счёта  292  17.3.3. Выбор тактов  17.4. Рекистру правления 1 ТІМ6 и ТІМ7 (ТІМх_СR1)  294  17.4.1. Регистру правления 1 ТІМ6 и ТІМ7 (ТІМХ_СR1)  294  17.4.2. Регистру правления 1 ТІМ6 и ТІМ7 (ТІМХ_СR1)  295  17.4.3. Регистру правления 1 ТІМ6 и ТІМ7 (ТІМХ_СR1)  296  17.4.4. Регистру правления 1 ТІМ6 и ТІМ7 (ТІМХ_СВ1)  297  17.4.3. Регистру правления 1 ТІМ6 и ТІМ7 (ТІМХ_СВ1)  298  17.4.4. Регистр разрешения прерываний ТІМ6 - ТІМ7 (ТІМХ_СВП)  299  17.4.4. Регистр состояния ТІМ6 - ТІМ7 (ТІМХ_СВП)  290  17.4.5. Регистр генерации событий ТІМ6 - ТІМ7 (ТІМХ_СВП)  291  17.4.7. Предделитель ТІМ6 - ТІМ7 (ТІМХ_СВП)  292  17.4.8. Регистр предзагрузки ТІМ6 - ТІМ7 (ТІМХ_АВП)  293  18.1. Введение в ВТС  18.2. Основные свойства ЯТС  18.3. Оункциональное описание ВТС  18.3.1. Обзор  18.3.2. Сброс регистров ВТС  18.3.3. Утение регистров ВТС  18.3.3. Учтение регистров ВТС  18.3.4. Конфигурация регистров ВТС  18.3.5. Установка флагов ВТС  18.3.5. Установка флагов ВТС  18.4. Регистры ЧТС  18.4. 1. Старший регистр управления ВТС (ВТС_СВН)  18.4.3. Регистры ЧТС  18.4. Регистры ЧТС  18.5. Карта регистров ВТС  18.5. Карта регистров ВТС  18.6. Регистры Фумльника ВТС (ВТС_СВН)  18.5. Карта регистров ВТС  19. Независимый сторожевой таймер (IWDG)  19.1. Введение в IWDG  19.3. 1. Аппаратный сторож  19.3. 2 Апиаратный сторож  19.3. 1. Регистр предделителя ВТС (ВТС_ОВН)  19.4. Регистры ПУСВ  19.4. Регистр предделителя (IWDG_PR)  19.4. Регистр предделителя (IWDG_PR)  19.4. Регистр предделителя (IWDG_PR)  19.4. Регистр предделителя ВСВ (ВСР)  19.4. Регистр предделителя (IWDG_PR)  19.4. Регистр преддели  |                                                                                                                       |            |

| 17.2. Основные свойства ТІМ6 и ТІМ7 17.3.1. Узел счёта 17.3.2. Режим счёта 290 17.3.3. Режим счёта 291 17.3.3. Выбор тактов 294 17.3.4. Режим отладки 294 17.4. Регистры ТІМ6 и ТІМ7 17.4.1. Регистр рарваления 1 ТІМ6 и ТІМ7 (ТІМх_СR1) 294 17.4.2. Регистр рарваления 2 (ТІМх_СR2) 295 17.4.3. Регистр разрешения прерываний ТІМ6 - ТІМ7 (ТІМх_DIER) 295 17.4.4. Регистр ревешения прерываний ТІМ6 - ТІМ7 (ТІМх_DIER) 296 17.4.5. Регистр генерации событий ТІМ6 - ТІМ7 (ТІМх_EGR) 297 17.4.7. Предделитель ТІМ6 - ТІМ7 (ТІМХ_CR2) 296 17.4.8. Регистр передарузки ТІМ6 - ТІМ7 (ТІМХ_ARR) 297 17.4.9. Карта регистров ТІМ6 - ТІМ7 (ТІМХ_ARR) 298 17.4.9. Карта регистров ТІМ6 - ТІМ7 297 18.1. Введение в RTC 297 18.2. Основные свойства RTC 297 18.3. Оункциональное описание RTC 298 18.3.2. Сброс регистров RTC 298 18.3.3. Чтение регистров RTC 298 18.3.3. Чтение регистров RTC 299 18.3.4. Конфигурация регистров RTC 299 18.3.5. Установка флагов RTC 299 18.4.1. Старший регистр управления RTC (RTC_CRH) 290 18.4.2. Младший регистр управления RTC (RTC_CRH) 291 18.4.3. Регистры STC 390 301 18.4.5. Регистры STC 390 302 18.4.6. Регистры БТС 304 19.1. Введение в IWDG 305 19.3.1. Аппаратный сторож ВТС 306 19.3.1. Аппаратный сторож ВТС 307 308 309 309 309 309 301 304 305 306 307 307 307 307 307 308 309 309 309 307 300 307 300 300 300 300 300 300 300                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | • • •                                                                                                                 |            |

| 17.3. Функциональное описание таймеров ТІМб и ТІМ7 17.3.1 Узел счёта 290 17.3.2. Режим очёта 292 17.3.3. Выбор тактов 294 17.4. Регистры ТІМб и ТІМ7 17.4.1 Регистр управления 2 (ТІМх_СR2) 17.4.4 Регистр управления 2 (ТІМх_СR2) 17.4.2 Регистр управления 2 (ТІМх_СR2) 17.4.3 Регистр разрешения прерываний ТІМб - ТІМ7 (ТІМх_DIER) 295 17.4.4.3 Регистр разрешения прерываний ТІМб - ТІМ7 (ТІМх_DIER) 295 17.4.5. Регистр тенерации событий ТІМб - ТІМ7 (ТІМХ_ERR) 296 17.4.6. Счётчик ТІМб - ТІМ7 (ТІМХ_СКТ) 296 17.4.7. Предделитель ТІМб - ТІМ7 (ТІМХ_ERC) 296 17.4.9. Карта регистров ТІМТ (ТІМХ_ERC) 297 18.1 Введение в RTC 297 18.1 Введение в RTC 18.2. Основные свойства RTC 18.3. Очункциональное описание RTC 298 18.3.1. Обзор 18.3.2. Сброс регистров RTC 298 18.3.3. Чтение регистров RTC 299 18.3.3. Чтение регистров RTC 299 18.3.4. Конфигурация регистров RTC 299 18.3.5. Установка флагов RTC 18.4. Регистры RTC 18.4.1. Старший регистр управления RTC (RTC_CRH) 18.4.2. Регистры Загрузки предделителя RTC (RTC_CRH) 18.4.3. Регистры загрузки предделителя RTC (RTC_CRH) 18.4.4. Регистры загрузки предделителя RTC (RTC_CRH) 18.4.5. Регистры очётчика RTC (RTC_CNTH / RTC_PRLL) 18.5. Карта регистров RTC 19.4.4. Регистры очётчика RTC (RTC_CRH) 18.4.5. Регистры очётчика RTC (RTC_CRH) 18.4.6. Регистры очётчика RTC (RTC_CNTH / RTC_CNTL) 18.5. Карта регистров RTC 19.1. Введение в IWDG 19.1. Введение в IWDG 19.3. Оункциональное описание IWDG 19.3. Оункциональное описание IWDG 19.3. Оункциональное описание IWDG 19.3. Оункциональное описание IWDG 19.4. Регистр предделителя RTC (RTC_CRH) 19.4. Регистр IWDG 19.4. Регистр IWDG 19.4. Регистр IWDG 19.4. Регистр Перделегиел RLR 19.4. Регистр пераделител RLR 19.4. Регистр Перделегиел  |                                                                                                                       |            |

| 17.3.1. Узел счёта 17.3.2. Режим счёта 17.3.3. Выбор тактов 17.3.4. Режим отладки 17.4. Регистры ТІМБ и ТІМ7 17.4.1. Регистру управления 1 ТІМБ и ТІМ7 (ТІМХ_СR1) 17.4.2. Регистру управления 1 ТІМБ и ТІМ7 (ТІМХ_СR1) 17.4.3. Регистр управления 1 ТІМБ и ТІМ7 (ТІМХ_СR1) 17.4.3. Регистр управления 1 ТІМБ - ТІМ7 (ТІМХ_СR1) 17.4.3. Регистр управления 1 ТІМБ - ТІМ7 (ТІМХ_СR1) 17.4.4. Регистр остояния ТІМБ - ТІМ7 (ТІМХ_СR) 17.4.5. Регистр генерации событий ТІМБ - ТІМ7 (ТІМХ_СВП) 17.4.5. Регистр генерации событий ТІМБ - ТІМ7 (ТІМХ_СВП) 17.4.6. Счётчик ТІМБ - ТІМ7 (ТІМХ_СВТ) 17.4.7. Предделитель ТІМБ - ТІМ7 (ТІМХ_СВТ) 17.4.9. Карта регистров ТІМБ - ТІМ7 (ТІМХ_СВТ) 17.4.9. Карта регистров ТІМБ - ТІМ7 (ТІМХ_СВТ) 18.1. Введение в ВТС 18.2. Основные свойства ВТС 18.3. Функциональное описание ВТС 18.3.1. Обзор 18.3.2. Сброс регистров ВТС 18.3.3. Чтение регистров ВТС 18.3.3. Чтение регистров ВТС 18.3.3. Установка флагов ВТС 18.4. Регистры ПТС 18.4. Гатарший регистр управления ВТС (ВТС_СВН) 18.4.1. Старший регистр управления ВТС (ВТС_СВН) 18.4.2. Младший регистр управления ВТС (ВТС_СВН) 18.4.3. Регистры Чтения предделителя ВТС (ВТС_СВН) 18.4.4. Регистры чтения предделителя ВТС (ВТС_СВН) 18.4.5. Регистры чтения предделителя ВТС (ВТС_СВН) 18.4.6. Регистры очётчика ВТС (ВТС_СВП) 18.4.7. Регистры очётчика ВТС (ВТС_СВП) 19. Независимый сторожевой таймер (IWDG) 19.1. Введение в IWDG 19.3. Функциональное описание IWDG 19.3. Функциональное описание IWDG 19.3.1. Аппаратный сторож 19.3.2. Защита доступа 19.4. Регистры IWDG 19.4.2. Регистр КПОД ВЦЯ 19.4.4. Регистр КПОД ВЦЯ 19.4.5. Регистр КПОД ВЦЯ 19.4.6. Регистр КПОД ВЦЯ 19.4.7. Регистр КПОД ВЦЯ 19.4.8. Регистр КПОД ВЦЯ 19.4.9. Регистр КПОД ВЦЯ 19.4.9. Регистр КПОД ВЦЯ 19.4.1. Регистр КПОД ВЦЯ 19.4.1. Регистр КПОД ВЦЯ 19.4.1. Регистр КПОД ВЦЯ 19.4.2. Регистр КПОД ВЦЯ 19.4.3.3.4. Регистр КПОД ВЦЯ 19.4.4. Регистр КПОД ВЦЯ 19.4.5. Регистр КПОД ВЦЯ 19.4.6. Регистр КПОД ВЦЯ 19.4.6. Регистр КПОД ВЦЯ 19.4.7. Регистр КПОД ВЦЯ 19.4.8. Регистр КПОД ВЦЯ 19.4.9. Регистр КПОД ВЦЯ 19.4.1. Регистр КПОД  |                                                                                                                       |            |

| 17.3.3. Выбор тактов 17.3.4. Режим отладки 17.4. Регистры ТІМБ и ТІМТ 17.4.1. Регистры ТІМБ и ТІМТ 17.4.1. Регистру пуравления 1 ТІМБ и ТІМ7 (ТІМХ_СR1) 17.4.2. Регистру разрешения прерываний ТІМБ - ТІМ7 (ТІМХ_СR1) 17.4.3. Регистр разрешения прерываний ТІМБ - ТІМ7 (ТІМХ_DIER) 17.4.4. Регистр разрешения прерываний ТІМБ - ТІМ7 (ТІМХ_DIER) 17.4.5. Регистр ренерации событий ТІМБ - ТІМ7 (ТІМХ_EGR) 17.4.5. Счётчик ТІМБ - ТІМ7 (ТІМХ_CRT) 17.4.7. Предделитель ТІМБ - ТІМ7 (ТІМХ_DIT) 17.4.8. Регистр предзагрузки ТІМБ - ТІМ7 (ТІМХ_ARR) 17.4.9. Карта регистров ТІМБ - ТІМ7 (ТІМХ_ARR) 18.1. Введение в ВТС 18.2. Основные свойства ВТС 18.3. Офункциональное описание ВТС 18.3. Офункциональное описание ВТС 18.3.1. Обзор 18.3.2. Сброс регистров ВТС 18.3.3. Чтение регистров ВТС 18.3.3. Чтение регистров ВТС 18.3.4. Конфигурация регистров ВТС 18.3.5. Установка флагов ВТС 18.4.1. Старший регистр управления ВТС (ВТС_CRH) 18.4.2. Регистры ВТС 18.4.3. Регистры загрузки предделителя ВТС (ВТС_CRH) 18.4.3. Регистры будильника ВТС (ВТС_CRH) 18.4.4. Регистры будильника ВТС (ВТС_CNTL) ЯТС_ИТL) 18.4.5. Карта регистров ВТС 19. Независимый сторожевой таймер (IWDG) 19.1. Введение в IWDG 19.3.1. Аппаратный сторож 19.3.2. Защита доступа 19.3.3. Режим отладки 19.4. Регистры IWDG 19.4.1. Регистр пераделителя (IWDG_PR) 19.4.2. Регистр пераделителя (IWDG_PR) 19.4.3. Регистр пераделителя (IWDG_PR) 19.4.4. Регистр пераделителя (IWDG_PR) 19.4.5. Карта регистров IWDG 20.0. Оконный сторожевой таймер (WWDG) 20.1. Введение в WWDG 20.2. Основные свойства WWDG 20.3. Функциональное описание WWDG 20.4. Вычисление в WWDG 20.4. Вычисление таймаута WWDG                                                                                                                                                                                                                                                                                           |                                                                                                                       |            |

| 17.3.4. Режим отладки 17.4. Регистры ТІМб и ТІМ7 17.4.1. Регистр управления 1 ТІМ6 и ТІМ7 (ТІМх_CR1) 17.4.2. Регистр управления 2 (ТІМХ_CR2) 17.4.3. Регистр разрешения прерываний ТІМ6 - ТІМ7 (ТІМХ_DIER) 295 17.4.4. Регистр состояния ТІМ6 - ТІМ7 (ТІМХ_SR) 295 17.4.5. Регистр ренорации событий ТІМ6 - ТІМ7 (ТІМХ_EGR) 296 17.4.6. Счётчик ТІМ6 - ТІМ7 (ТІМХ_CRT) 296 17.4.7. Предделитель ТІМ6 - ТІМ7 (ТІМХ_PSC) 297 17.4.8. Регистр предзагрузки ТІМ6 - ТІМ7 (ТІМХ_ARR) 297 17.4.9. Карта регистров ТІМ6 - ТІМ7 (ТІМХ_ARR) 297 18.1. Введение в ВТС 297 18.1. Введение в ВТС 297 18.3. Офукциональное описание RTC 18.3. Основные свойства ВТС 298 18.3.3. Утение регистров ВТС 18.3.4. Конфигурация регистров ВТС 298 18.3.5. Установка флагов ВТС 299 18.3.5. Установка флагов ВТС 291 18.4. Регистры ВТС 291 18.4. Отарший регистр управления ВТС (ВТС_CRH) 293 18.4. Отарший регистр управления ВТС (ВТС_CRH) 294 18.4. Регистры загрузки предделителя ВТС (ВТС_CRH) 295 18.4. Регистры офуцильника ВТС (ВТС_DVH / ЯТС_DIVL) 296 297 298 299 299 290 200 200 200 200 200 200 200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                       |            |

| 17.4. Регистры ТІМ6 и ТІМ7 17.4.1. Регистру управления 1 ТІМ6 и ТІМ7 (ТІМх_СR1) 17.4.2. Регистр управления 2 (ТІМх_СR2) 295 17.4.3. Регистр управления 2 (ТІМх_СR2) 295 17.4.3. Регистр управления 2 (ТІМх_СR2) 295 17.4.4. Регистр разрешения прерываний ТІМ6 - ТІМ7 (ТІМх_DIER) 296 17.4.6. Регистр генерации событий ТІМ6 - ТІМ7 (ТІМХ_ER) 296 17.4.6. Счётчик ТІМ6 - ТІМ7 (ТІМХ_СМТ) 296 17.4.7. Предделитель ТІМ6 - ТІМ7 (ТІМХ_СВТ) 297 17.4.8. Регистр предзагрузки ТІМ6 - ТІМ7 (ТІМХ_АRR) 298 17.4.9. Карта регистров ТІМ6 - ТІМ7 (ТІМХ_АRR) 297 18. Таймер реального времени (RTC) 297 18.1. Введение в RTC 297 18.2. Основные свойства RTC 298 18.3.2. Основные свойства RTC 298 18.3.3. Функциональное описание RTC 298 18.3.3. Установка флагов RTC 299 18.3.3. Установка флагов RTC 299 18.3.4. Конфигурация регистров RTC 299 18.3.5. Установка флагов RTC 299 18.4.1. Старший регистр управления RTC (RTC_CRH) 294 18.4.2. Младший регистр управления RTC (RTC_CRH) 294 18.4.3. Регистры Sarpyзки предделителя RTC (RTC_PRLH / RTC_PRLL) 296 18.4.4. Регистры чейтчика RTC (RTC_CRH) 297 18.5. Карта регистров RTC 300 18.5. Карта регистров RTC 301 302 18.5. Карта регистров RTC 303 304 19.1. Введение в IWDG 305 19.3. Функциональное описание IWDG 306 19.3. Функциональное описание IWDG 307 307 308 309 309 309 309 300 300 300 300 300 300                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ·                                                                                                                     |            |