Здравствуйте, гость ( Вход | Регистрация )

| SuperMax |

18.10.2015, 11:37 18.10.2015, 11:37

Сообщение

#1

|

Администратор      Группа: Root Admin Сообщений: 6 377 Регистрация: 7.1.2006 Из: Красноярск Пользователь №: 1 |

Dig my grave both long and narrow  Make my coffin neat and strong Make my coffin neat and strong (из старой американской песни) (из старой американской песни) Вступление  Данный труд открывает цикл статей, посвящённых процессорам и архитектуре Alpha, а также многому с ними связанному. Цикл, потому что изложение всего имеющегося материала в виде одного обзора показалось автору довольно проблематичным и неуместным. К тому же, открываемая тема является действительно многогранной и во многих аспектах фундаментальной, не имеющей прецедентов в плане полноты и масштабности изложения, поэтому вполне заслуживает пристального и подробного рассмотрения. Возможно, эта и последующие статьи смотрелись бы более уместно лет 5 назад, когда Alpha-процессоры ставили очередные рекорды производительности и масштабируемости, a их будущее ожидалось совсем не таким, каким оно выглядит с точки зрения дня сегодняшнего. Однако, именно в наше время можно уверенно подвести финальную черту под этой сагой, посвященной одной из самых интересных и перспективных компьютерных архитектур. Данный труд открывает цикл статей, посвящённых процессорам и архитектуре Alpha, а также многому с ними связанному. Цикл, потому что изложение всего имеющегося материала в виде одного обзора показалось автору довольно проблематичным и неуместным. К тому же, открываемая тема является действительно многогранной и во многих аспектах фундаментальной, не имеющей прецедентов в плане полноты и масштабности изложения, поэтому вполне заслуживает пристального и подробного рассмотрения. Возможно, эта и последующие статьи смотрелись бы более уместно лет 5 назад, когда Alpha-процессоры ставили очередные рекорды производительности и масштабируемости, a их будущее ожидалось совсем не таким, каким оно выглядит с точки зрения дня сегодняшнего. Однако, именно в наше время можно уверенно подвести финальную черту под этой сагой, посвященной одной из самых интересных и перспективных компьютерных архитектур.  Эта статья является, в значительной мере, историческим очерком с элементами анализа, поэтому её следует рассматривать именно в этом аспекте. В целом, она не претендует на универсальность, хотя и содержит значительное количество справочной информации. С другой стороны, рассматривать её как некролог или надгробную молитву также явно не стоит... Эта статья является, в значительной мере, историческим очерком с элементами анализа, поэтому её следует рассматривать именно в этом аспекте. В целом, она не претендует на универсальность, хотя и содержит значительное количество справочной информации. С другой стороны, рассматривать её как некролог или надгробную молитву также явно не стоит... -------------------- Живы будем - Не помрем !

|

|

Ответов

| SuperMax |

18.10.2015, 14:39 18.10.2015, 14:39

Сообщение

#2

|

Администратор      Группа: Root Admin Сообщений: 6 377 Регистрация: 7.1.2006 Из: Красноярск Пользователь №: 1 |

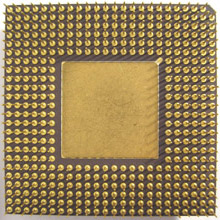

Часть 4. EV4, LCA4, EV45, LCA45  Первый процессор из семейства Alpha получил название 21064 (21 указывал, что Alpha -- это архитектура XXI века, 0 -- процессорное поколение, 64 -- разрядность в битах), и кодовое наименование EV4 (EV является [предположительно] аббревиатурой "Extended VAX", а цифра 4 -- поколением техпроцесса, CMOS4; CMOS, в свою очередь, есть аббревиатура "Complementary Metal Oxide Semiconductor"). Стоит отметить, что прототип EV4 был готов ещё в 1991, по CMOS3 техпроцессу, а поэтому с уменьшенными кэшами и без блока вычислений с плавающей запятой; тем не менее, он сыграл свою роль в отладке архитектуры и программной среды. EV4 был представлен в ноябре 1992, и поступил в производство на передовом для того времени 3-слойном 0,75µ техпроцессе (впоследствии, производство было переведено на оптическую модификацию CMOS4 -- CMOS4S, 0,675µ). Был рассчитан на напряжение питания в 3,3В, выпускался с тактовыми частотами от 150МГц до 200МГц (ТDP от 21Вт до 27Вт). Состоял из 1,68 млн. транзисторов, и имел площадь ядра в 233 кв.мм. Поддерживал многопроцессорность, как один из ключевых моментов архитектуры. Форм-фактор: PGA-431 (Pin Grid Array). Первый процессор из семейства Alpha получил название 21064 (21 указывал, что Alpha -- это архитектура XXI века, 0 -- процессорное поколение, 64 -- разрядность в битах), и кодовое наименование EV4 (EV является [предположительно] аббревиатурой "Extended VAX", а цифра 4 -- поколением техпроцесса, CMOS4; CMOS, в свою очередь, есть аббревиатура "Complementary Metal Oxide Semiconductor"). Стоит отметить, что прототип EV4 был готов ещё в 1991, по CMOS3 техпроцессу, а поэтому с уменьшенными кэшами и без блока вычислений с плавающей запятой; тем не менее, он сыграл свою роль в отладке архитектуры и программной среды. EV4 был представлен в ноябре 1992, и поступил в производство на передовом для того времени 3-слойном 0,75µ техпроцессе (впоследствии, производство было переведено на оптическую модификацию CMOS4 -- CMOS4S, 0,675µ). Был рассчитан на напряжение питания в 3,3В, выпускался с тактовыми частотами от 150МГц до 200МГц (ТDP от 21Вт до 27Вт). Состоял из 1,68 млн. транзисторов, и имел площадь ядра в 233 кв.мм. Поддерживал многопроцессорность, как один из ключевых моментов архитектуры. Форм-фактор: PGA-431 (Pin Grid Array).  Кэш L1 был интегрирован: 8Кб для инструкций (I-cache, instruction cache), с прямым отображением (direct-mapped), а также 8Кб для данных (D-cache, data cache), с прямым отображением и сквозной записью (write-through). Задержки при чтении из D-cache составляли 3 такта. Каждая линия I-cache состояла из 32 байт инструкций, 21-битного тега, 8-битного поля истории переходов, и нескольких вспомогательных полей; каждая линия D-cache состояла из 32 байт данных и 21-битного тега. Кэш L2 (B-cache, backup cache) был рекомендуемой опцией, набирался на микросхемах синхронной или асинхронной статической памяти, работал в режиме обратной записи (write-back) с прямым отображением и упреждающим чтением (read-ahead), мог иметь размер до 16Мб (обычно от 512Кб до 2Мб); каждая линия состояла из 32 байт данных или инструкций с 1-битным long-word parity или 7-битным long-word ECC, максимум 17-битного тега с 1 битом чётности, и 3 битов состояния с 1 битом четности. Скорость чтения/записи B-cache программировалась, в тактах процессора. Разрядность системной шины данных составляла 64 или 128 бит (программируемо, с 1-битным long-word parity или 7-битным long-word ECC), и она мультиплексировалась с шиной данных B-cache, переключаясь при необходимости; разрядность системной шины адреса составляла 34 бита. Организационно B-cache был включающим (inclusive) D-cache, то есть поддерживал копию содержимого последнего. При выгрузке данных из B-cache в память использовался механизм victim write. Операции чтения/записи в B-cache являлись прерогативой исключительно процессора, для системной логики было разрешено только чтение файла тегов (B-tag, что жизненно необходимо особенно в многопроцессорных системах, для обеспечения согласованности (когерентности) кэшей). Кэш L1 был интегрирован: 8Кб для инструкций (I-cache, instruction cache), с прямым отображением (direct-mapped), а также 8Кб для данных (D-cache, data cache), с прямым отображением и сквозной записью (write-through). Задержки при чтении из D-cache составляли 3 такта. Каждая линия I-cache состояла из 32 байт инструкций, 21-битного тега, 8-битного поля истории переходов, и нескольких вспомогательных полей; каждая линия D-cache состояла из 32 байт данных и 21-битного тега. Кэш L2 (B-cache, backup cache) был рекомендуемой опцией, набирался на микросхемах синхронной или асинхронной статической памяти, работал в режиме обратной записи (write-back) с прямым отображением и упреждающим чтением (read-ahead), мог иметь размер до 16Мб (обычно от 512Кб до 2Мб); каждая линия состояла из 32 байт данных или инструкций с 1-битным long-word parity или 7-битным long-word ECC, максимум 17-битного тега с 1 битом чётности, и 3 битов состояния с 1 битом четности. Скорость чтения/записи B-cache программировалась, в тактах процессора. Разрядность системной шины данных составляла 64 или 128 бит (программируемо, с 1-битным long-word parity или 7-битным long-word ECC), и она мультиплексировалась с шиной данных B-cache, переключаясь при необходимости; разрядность системной шины адреса составляла 34 бита. Организационно B-cache был включающим (inclusive) D-cache, то есть поддерживал копию содержимого последнего. При выгрузке данных из B-cache в память использовался механизм victim write. Операции чтения/записи в B-cache являлись прерогативой исключительно процессора, для системной логики было разрешено только чтение файла тегов (B-tag, что жизненно необходимо особенно в многопроцессорных системах, для обеспечения согласованности (когерентности) кэшей).  Процессор имел один целочисленный конвейер (E-box, 7 стадий), и один вещественный конвейер (F-box, 10 стадий). Декодер и планировщик инструкций (I-box) был в состоянии подавать 2 команды за такт в порядке очереди (in-order) на исполняющие устройства, то есть на E-box, F-box и блок загрузки/сохранения (A-box). Контроллер кэшей и системной шины (C-box) работал в тесном взаимодействии с A-box и управлял как интегрированными I-cache и D-cache, так и внешним B-cache. Также присутствовал блок предсказания переходов (branch prediction unit), с таблицей переходов на 4096 записей (branch history table), по 2 бита каждая. I-TLB имел 8 записей для 8Кб-страниц, и 4 записи для 4Мб-страниц, все с пoлной ассоциативностью (fully-associative). D-TLB имел 32 записи, с полной ассоциативностью. Процессор имел один целочисленный конвейер (E-box, 7 стадий), и один вещественный конвейер (F-box, 10 стадий). Декодер и планировщик инструкций (I-box) был в состоянии подавать 2 команды за такт в порядке очереди (in-order) на исполняющие устройства, то есть на E-box, F-box и блок загрузки/сохранения (A-box). Контроллер кэшей и системной шины (C-box) работал в тесном взаимодействии с A-box и управлял как интегрированными I-cache и D-cache, так и внешним B-cache. Также присутствовал блок предсказания переходов (branch prediction unit), с таблицей переходов на 4096 записей (branch history table), по 2 бита каждая. I-TLB имел 8 записей для 8Кб-страниц, и 4 записи для 4Мб-страниц, все с пoлной ассоциативностью (fully-associative). D-TLB имел 32 записи, с полной ассоциативностью.   Несмотря на отличную производительность, EV4 был довольно дорог для значительной части потенциальных покупателей, и поэтому в сентябре 1993 был анонсирован его бюджетный собрат, 21066 (LCA4, или LCA4S). Этот процессор был основан на ядре 21064, но с дополнительно интегрированными контроллерами памяти и шины PCI, а также некоторыми второстепенными функциями. Однако, разрядность системной шины данных была урезана до 64 бит, что негативно сказалось на производительности. LCA4 производился по 0,675µ CMOS4S техпроцессу, и его площадь оказалась ещё меньше, чем у EV4 (209 кв.мм по сравнению с 234 кв.мм.), а тактовые частоты были занижены (от 100МГц до 166МГц), в значительной мере из-за потенциальной угрозы перегрева в плохо вентилируемых настольных системных блоках того времени, и чтобы не создавать дополнительной конкуренции EV4. Количество транзисторов в ядре составило 1,75 млн., a напряжение питания -- 3,3В. Дизайн этого процессора был лицензирован Mitsubishi, и последняя также производила LCA4 (включая и 200МГц версию).   В октябре 1993, на Microprocessor Forum, был анонсирован 21064А (EV45), обновленная версия EV4, производимая по 4-слойному 0,5µ CMOS5 техпроцессу. В ноябре 1994, на COMDEX'94, был представлен 21066А (LCA45), почти аналогично модифицированная версия LCA4. Стоит отметить, что манера маркетологов DEC добавлять букву к модели процессора при перепланировке ядра под новый техпроцесс сохранилась и в будущем. Собственно состав процессорных ядер изменился незначительно; EV45 теперь обладал удвоенным размером кэша L1 (16Кб I-cache + 16Кб D-cache), к полям данных и тегам I-cache и D-cache было добавлено по биту чётности, поля истории переходов I-cache были расширены до 16 бит, ассоциативность D-cache была увеличена до 2 (2-way set associative), а к режимам контроля над системной шиной данных был добавлен 1-битный byte parity. Также в EV45 и LCA45 был незначительно модифицирован F-box (оптимизация деления: в EV4 одна операция требовала 34 такта для операндов одинарной точности и 63 такта для операндов двойной точности, вне зависимости от значений операндов; в EV45 она уже требовала от 19 до 34 тактов для операндов одинарной точности и от 29 до 63 тактов для операндов двойной точности, в зависимости от значений операндов). LCA45 также производился на мощностях Mitsubishi. Площади ядер уменьшились: до 164 кв.мм (EV45) и до 161 кв.мм (LCA45), количество транзисторов в ядре EV45 возросло до 2,85 млн., а в ядре LCA45 осталось прежним (1,75 млн.). В конечном результате, энергопотребление обоих процессоров в расчёте на единицу частоты сократилось, хотя напряжение питания осталось неизменным (3,3В). Тактовые частоты ЕV45 составляли от 200МГц до 300МГц (TDP от 24Вт до 36Вт), LCA45 -- от 166 до 233МГц. В октябре 1993, на Microprocessor Forum, был анонсирован 21064А (EV45), обновленная версия EV4, производимая по 4-слойному 0,5µ CMOS5 техпроцессу. В ноябре 1994, на COMDEX'94, был представлен 21066А (LCA45), почти аналогично модифицированная версия LCA4. Стоит отметить, что манера маркетологов DEC добавлять букву к модели процессора при перепланировке ядра под новый техпроцесс сохранилась и в будущем. Собственно состав процессорных ядер изменился незначительно; EV45 теперь обладал удвоенным размером кэша L1 (16Кб I-cache + 16Кб D-cache), к полям данных и тегам I-cache и D-cache было добавлено по биту чётности, поля истории переходов I-cache были расширены до 16 бит, ассоциативность D-cache была увеличена до 2 (2-way set associative), а к режимам контроля над системной шиной данных был добавлен 1-битный byte parity. Также в EV45 и LCA45 был незначительно модифицирован F-box (оптимизация деления: в EV4 одна операция требовала 34 такта для операндов одинарной точности и 63 такта для операндов двойной точности, вне зависимости от значений операндов; в EV45 она уже требовала от 19 до 34 тактов для операндов одинарной точности и от 29 до 63 тактов для операндов двойной точности, в зависимости от значений операндов). LCA45 также производился на мощностях Mitsubishi. Площади ядер уменьшились: до 164 кв.мм (EV45) и до 161 кв.мм (LCA45), количество транзисторов в ядре EV45 возросло до 2,85 млн., а в ядре LCA45 осталось прежним (1,75 млн.). В конечном результате, энергопотребление обоих процессоров в расчёте на единицу частоты сократилось, хотя напряжение питания осталось неизменным (3,3В). Тактовые частоты ЕV45 составляли от 200МГц до 300МГц (TDP от 24Вт до 36Вт), LCA45 -- от 166 до 233МГц.  Так как DEC участвовала в разработках оборудования под заказ Министерства обороны США, то в 1994 были спроектированы процессоры 21068 (66МГц) и 21068А (100МГц), являвшиеся вариантами LCA4 и LCA45, адаптированными под военные нужды (пассивное охлаждение, жёсткие температурные условия, пр.). Так как DEC участвовала в разработках оборудования под заказ Министерства обороны США, то в 1994 были спроектированы процессоры 21068 (66МГц) и 21068А (100МГц), являвшиеся вариантами LCA4 и LCA45, адаптированными под военные нужды (пассивное охлаждение, жёсткие температурные условия, пр.).   Первые чипсеты для EV4 использовали периферийные шины TURBOchannel, FutureBus+ и XMI. Хотя все эти реализации были очень скоростными для своего времени (около 100Мб/с на шину), они не получили широкого распространения, и количество доступной периферии измерялось единицами. Поэтому DEC обратила внимание на стандартные шинные архитектуры, такие как PCI и ISA (EISA). В начале 1994 был представлен чипсет DEC Apecs в двух исполнениях: с 64-битной системной шиной данных (21071) и 128-битной (21072). Вся разница между ними состояла в том, что 21071 состоял из 4 миросхем (1 универсальный контроллер, 2 микросхемы data slice, 1 контроллер шины PCI), а 21072 -- из 6 (дополнительно ещё 2 микросхемы data slice). Поддерживал частоту системной шины в 33МГц, до 16Мб B-cache и до 4Гб памяти FPM parity со временем доступа от 100 до 50нс. Поддержка шин ISA или EISA могла быть реализована посредством стандартных мостов, таких как i82378IB (ISA) или i82378EB (EISA). Первые чипсеты для EV4 использовали периферийные шины TURBOchannel, FutureBus+ и XMI. Хотя все эти реализации были очень скоростными для своего времени (около 100Мб/с на шину), они не получили широкого распространения, и количество доступной периферии измерялось единицами. Поэтому DEC обратила внимание на стандартные шинные архитектуры, такие как PCI и ISA (EISA). В начале 1994 был представлен чипсет DEC Apecs в двух исполнениях: с 64-битной системной шиной данных (21071) и 128-битной (21072). Вся разница между ними состояла в том, что 21071 состоял из 4 миросхем (1 универсальный контроллер, 2 микросхемы data slice, 1 контроллер шины PCI), а 21072 -- из 6 (дополнительно ещё 2 микросхемы data slice). Поддерживал частоту системной шины в 33МГц, до 16Мб B-cache и до 4Гб памяти FPM parity со временем доступа от 100 до 50нс. Поддержка шин ISA или EISA могла быть реализована посредством стандартных мостов, таких как i82378IB (ISA) или i82378EB (EISA).  Первая рабочая станция архитектуры Alpha от DEC была выпущена в ноябре 1992, DEC 3000 Model 500 AXP (кодовое имя Flamingo), с процессором EV4 150МГц, 512Кб B-cache, 32Мб оперативной памяти, SCSI HDD на 1Гб, SCSI CD-ROM, встроенным контроллером Ethernet 10Мбит (толстый коаксиал и витая пара), встроенным звуковым и ISDN контроллером, а также с 19-дюймовым монитором (1280х1024 8-бит). Цена была шокирующая: 38995 долл. США. Первая рабочая станция архитектуры Alpha от DEC была выпущена в ноябре 1992, DEC 3000 Model 500 AXP (кодовое имя Flamingo), с процессором EV4 150МГц, 512Кб B-cache, 32Мб оперативной памяти, SCSI HDD на 1Гб, SCSI CD-ROM, встроенным контроллером Ethernet 10Мбит (толстый коаксиал и витая пара), встроенным звуковым и ISDN контроллером, а также с 19-дюймовым монитором (1280х1024 8-бит). Цена была шокирующая: 38995 долл. США.  -------------------- Живы будем - Не помрем !

|

Сообщений в этой теме

SuperMax Alpha: история в фактах и комментариях 18.10.2015, 11:37

SuperMax Alpha: история в фактах и комментариях 18.10.2015, 11:37

SuperMax [b]

Часть 1. PDP и VAX

[b]Digital Equipment Corp... 18.10.2015, 14:35

SuperMax [b]

Часть 1. PDP и VAX

[b]Digital Equipment Corp... 18.10.2015, 14:35

SuperMax [b]Часть 2. Проект PRISM

[img]http://www1.fcenter.... 18.10.2015, 14:35

SuperMax [b]Часть 2. Проект PRISM

[img]http://www1.fcenter.... 18.10.2015, 14:35

SuperMax [b]Часть 5. EV5, EV56, PCA56, PCA57

[img]http://ww... 18.10.2015, 14:44

SuperMax [b]Часть 5. EV5, EV56, PCA56, PCA57

[img]http://ww... 18.10.2015, 14:44

SuperMax [b]Часть 6. Крах DEC

[img]http://www1.fcenter.ru/i... 18.10.2015, 14:46

SuperMax [b]Часть 6. Крах DEC

[img]http://www1.fcenter.ru/i... 18.10.2015, 14:46

SuperMax [b]Часть 7. EV6, EV67, EV68C, EV68A

[img]http://ww... 18.10.2015, 14:55

SuperMax [b]Часть 7. EV6, EV67, EV68C, EV68A

[img]http://ww... 18.10.2015, 14:55

SuperMax [b]Часть 8. Эпоха Compaq

[img]http://www1.fcenter.... 18.10.2015, 14:57

SuperMax [b]Часть 8. Эпоха Compaq

[img]http://www1.fcenter.... 18.10.2015, 14:57

SuperMax Часть 9. EV7, EV79, EV7z, EV8

http://www1.fcenter.... 18.10.2015, 14:59

SuperMax Часть 9. EV7, EV79, EV7z, EV8

http://www1.fcenter.... 18.10.2015, 14:59

SuperMax [b]Литература

1. Rich Witek, Dick Sites. Alpha Ar... 18.10.2015, 15:02

SuperMax [b]Литература

1. Rich Witek, Dick Sites. Alpha Ar... 18.10.2015, 15:02  |

1 чел. читают эту тему (гостей: 1, скрытых пользователей: 0)

Пользователей: 0

| Текстовая версия | Сейчас: 13.5.2026, 12:18 |