Здравствуйте, гость ( Вход | Регистрация )

| SuperMax |

18.10.2015, 11:37 18.10.2015, 11:37

Сообщение

#1

|

Администратор      Группа: Root Admin Сообщений: 6 377 Регистрация: 7.1.2006 Из: Красноярск Пользователь №: 1 |

Dig my grave both long and narrow  Make my coffin neat and strong Make my coffin neat and strong (из старой американской песни) (из старой американской песни) Вступление  Данный труд открывает цикл статей, посвящённых процессорам и архитектуре Alpha, а также многому с ними связанному. Цикл, потому что изложение всего имеющегося материала в виде одного обзора показалось автору довольно проблематичным и неуместным. К тому же, открываемая тема является действительно многогранной и во многих аспектах фундаментальной, не имеющей прецедентов в плане полноты и масштабности изложения, поэтому вполне заслуживает пристального и подробного рассмотрения. Возможно, эта и последующие статьи смотрелись бы более уместно лет 5 назад, когда Alpha-процессоры ставили очередные рекорды производительности и масштабируемости, a их будущее ожидалось совсем не таким, каким оно выглядит с точки зрения дня сегодняшнего. Однако, именно в наше время можно уверенно подвести финальную черту под этой сагой, посвященной одной из самых интересных и перспективных компьютерных архитектур. Данный труд открывает цикл статей, посвящённых процессорам и архитектуре Alpha, а также многому с ними связанному. Цикл, потому что изложение всего имеющегося материала в виде одного обзора показалось автору довольно проблематичным и неуместным. К тому же, открываемая тема является действительно многогранной и во многих аспектах фундаментальной, не имеющей прецедентов в плане полноты и масштабности изложения, поэтому вполне заслуживает пристального и подробного рассмотрения. Возможно, эта и последующие статьи смотрелись бы более уместно лет 5 назад, когда Alpha-процессоры ставили очередные рекорды производительности и масштабируемости, a их будущее ожидалось совсем не таким, каким оно выглядит с точки зрения дня сегодняшнего. Однако, именно в наше время можно уверенно подвести финальную черту под этой сагой, посвященной одной из самых интересных и перспективных компьютерных архитектур.  Эта статья является, в значительной мере, историческим очерком с элементами анализа, поэтому её следует рассматривать именно в этом аспекте. В целом, она не претендует на универсальность, хотя и содержит значительное количество справочной информации. С другой стороны, рассматривать её как некролог или надгробную молитву также явно не стоит... Эта статья является, в значительной мере, историческим очерком с элементами анализа, поэтому её следует рассматривать именно в этом аспекте. В целом, она не претендует на универсальность, хотя и содержит значительное количество справочной информации. С другой стороны, рассматривать её как некролог или надгробную молитву также явно не стоит... -------------------- Живы будем - Не помрем !

|

|

Ответов

| SuperMax |

18.10.2015, 14:44 18.10.2015, 14:44

Сообщение

#2

|

Администратор      Группа: Root Admin Сообщений: 6 377 Регистрация: 7.1.2006 Из: Красноярск Пользователь №: 1 |

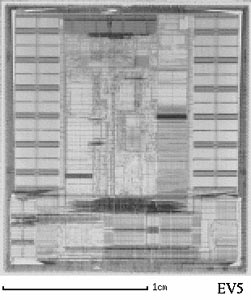

Часть 5. EV5, EV56, PCA56, PCA57  Первая архитектурная информация о своём Alpha-процессоре 2-го поколения была открыта DEC на конференции Hot Chips, которая состоялась 14 августа 1994 в Пало-Альто (Калифорния), хотя официальным анонсом 21164 (EV5) можно считать пресс-релиз DEC от 7 сентября 1994. Процессор базировался на ядре EV45 и содержал изменения скорее экстенсивного характера, чем интенсивного. Ядро включало удвоенное количество конвейеров для целочисленной и вещественной математики (по сравнению с EV4 или EV45), причём количество стадий вещественных конвейеров сократилось с 10 до 9. Однако, целочисленные конвейеры были неодинаковы: хотя оба могли выполнять элементарные арифметические и логические операции, только в компетенцию 1-го входило выполнение инструкций умножения и смещения, и только по 2-му могли быть направлены инструкции условных/безусловных переходов; также, оба конвейера могли вычислять виртуальные адреса для команд загрузки, однако только 1-й -- для команд сохранения. Вещественные конвейеры были также неоднородны: 1-й мог выполнять любой код с плавающей запятой, кроме инструкций умножения, которые были теми единственными командами, что мог выполнять 2-й конвейер. Чтобы обеспечить эффективную загрузку функциональных устройств, I-box мог выбирать и декодировать до 4 инструкций за такт. Производился по тому же 4-слойному 0,5µ CMOS5 техпроцессу, что и EV45, был рассчитан на напряжение питания в 3,3В, имел площадь ядра в 299 кв.мм. и содержал 9,3 млн. транзисторов (из них 7,8 млн. в виде интегрированного кэша), что было очень близко к теоретическому пределу для данного техпроцесса. Тактовые частоты EV5 составляли от 266МГц до 333МГц (TDP от 46Вт до 56Вт). Форм-фактор: IPGA-499 (Interstitial Pin Grid Array). Первая архитектурная информация о своём Alpha-процессоре 2-го поколения была открыта DEC на конференции Hot Chips, которая состоялась 14 августа 1994 в Пало-Альто (Калифорния), хотя официальным анонсом 21164 (EV5) можно считать пресс-релиз DEC от 7 сентября 1994. Процессор базировался на ядре EV45 и содержал изменения скорее экстенсивного характера, чем интенсивного. Ядро включало удвоенное количество конвейеров для целочисленной и вещественной математики (по сравнению с EV4 или EV45), причём количество стадий вещественных конвейеров сократилось с 10 до 9. Однако, целочисленные конвейеры были неодинаковы: хотя оба могли выполнять элементарные арифметические и логические операции, только в компетенцию 1-го входило выполнение инструкций умножения и смещения, и только по 2-му могли быть направлены инструкции условных/безусловных переходов; также, оба конвейера могли вычислять виртуальные адреса для команд загрузки, однако только 1-й -- для команд сохранения. Вещественные конвейеры были также неоднородны: 1-й мог выполнять любой код с плавающей запятой, кроме инструкций умножения, которые были теми единственными командами, что мог выполнять 2-й конвейер. Чтобы обеспечить эффективную загрузку функциональных устройств, I-box мог выбирать и декодировать до 4 инструкций за такт. Производился по тому же 4-слойному 0,5µ CMOS5 техпроцессу, что и EV45, был рассчитан на напряжение питания в 3,3В, имел площадь ядра в 299 кв.мм. и содержал 9,3 млн. транзисторов (из них 7,8 млн. в виде интегрированного кэша), что было очень близко к теоретическому пределу для данного техпроцесса. Тактовые частоты EV5 составляли от 266МГц до 333МГц (TDP от 46Вт до 56Вт). Форм-фактор: IPGA-499 (Interstitial Pin Grid Array).  Размеры и организация I-cache и D-cache остались как у EV4, то есть по 8Кб, и со сквозной записью для D-cache, хотя он теперь стал двухпортовым по чтению, то есть за 1 такт он мог поставить данные для 2 инструкций загрузки. Жертвуя транзисторами во имя быстродействия, физически D-cache состоял из 2 абсолютно одинаковых по содержанию частей размером в 8Кб каждая, то есть чтение шло из любой части, а запись -- одновременно в обе. Так как процессор имел 96Кб интегрированного кэша L2 с обратной записью с 3-канальной ассоциативностью, то в структуру C-box была добавлена его поддержка (S-cache, secondary cache) через независимую 128-битную шину данных, при этом интерфейс к внешнему B-cache (который все ещё оставался опциональным, набирался на микросхемах синхронной статической памяти и мог иметь размер до 64Мб, хотя обычно составлял от 1Мб до 4Мб) был сохранён -- другими словами, EV5 поддерживал 3 уровня кэшей. Доступ к S-cache был организован по принципу 4-стадийного конвейера: два такта на поиск тега и его изменение, два такта на доступ к данным и их передачу; строка S-cache была в 64 байта (с возможным разделением на две 32-байтных подстроки), с одним тегом на строку. Задержки при чтении из D-cache сократились до 2 тактов, а из S-cache -- составляли 7 тактов (как упоминалось выше, 4 такта на первые 16 байт, и по 1 такту на каждые последующие 16 байт для формирования полной строки). Как и в EV4, содержимое D-cache дублировалось, только теперь в S-cache; в свою очередь, для упрощения поддержки, B-cache был включающим S-cache, несмотря на разницу в ассоциативностях. Ёмкость I-TLB была увеличена до 48 записей (страницы размером от 8Кб до 4Мб), а D-TLB -- до 64 записей, причём он стал двухпортовым (по аналогии с D-cache). Системная шина данных имела фиксированную ширину в 128 бит (с дополнительными 16 битами для ECC) и всё так же мультиплексировалась с шиной данных к B-cache; системная шина адреса была 40-битной, управления -- 10-битной. Размеры и организация I-cache и D-cache остались как у EV4, то есть по 8Кб, и со сквозной записью для D-cache, хотя он теперь стал двухпортовым по чтению, то есть за 1 такт он мог поставить данные для 2 инструкций загрузки. Жертвуя транзисторами во имя быстродействия, физически D-cache состоял из 2 абсолютно одинаковых по содержанию частей размером в 8Кб каждая, то есть чтение шло из любой части, а запись -- одновременно в обе. Так как процессор имел 96Кб интегрированного кэша L2 с обратной записью с 3-канальной ассоциативностью, то в структуру C-box была добавлена его поддержка (S-cache, secondary cache) через независимую 128-битную шину данных, при этом интерфейс к внешнему B-cache (который все ещё оставался опциональным, набирался на микросхемах синхронной статической памяти и мог иметь размер до 64Мб, хотя обычно составлял от 1Мб до 4Мб) был сохранён -- другими словами, EV5 поддерживал 3 уровня кэшей. Доступ к S-cache был организован по принципу 4-стадийного конвейера: два такта на поиск тега и его изменение, два такта на доступ к данным и их передачу; строка S-cache была в 64 байта (с возможным разделением на две 32-байтных подстроки), с одним тегом на строку. Задержки при чтении из D-cache сократились до 2 тактов, а из S-cache -- составляли 7 тактов (как упоминалось выше, 4 такта на первые 16 байт, и по 1 такту на каждые последующие 16 байт для формирования полной строки). Как и в EV4, содержимое D-cache дублировалось, только теперь в S-cache; в свою очередь, для упрощения поддержки, B-cache был включающим S-cache, несмотря на разницу в ассоциативностях. Ёмкость I-TLB была увеличена до 48 записей (страницы размером от 8Кб до 4Мб), а D-TLB -- до 64 записей, причём он стал двухпортовым (по аналогии с D-cache). Системная шина данных имела фиксированную ширину в 128 бит (с дополнительными 16 битами для ECC) и всё так же мультиплексировалась с шиной данных к B-cache; системная шина адреса была 40-битной, управления -- 10-битной.   В октябре 1995, на Microprocessor Forum, был представлен 21164А (EV56), незначительно модифицированная версия EV5 с учетом 0,35µ конструкторских норм (CMOS6), производимая на той же фабрике в Хадсоне (DEC инвестировала в её модернизацию около 450 млн. долл США). Наиболее существенным архитектурным отличием можно считать BWX (Byte-Word Extension) -- набор из 6 дополнительных команд для загрузки/сохранения данных размером в 8 или 16 бит. Изначально архитектура Alpha поддерживала загрузку/сохранение данных квантами исключительно по 32 или 64 бита, что создавало определенные сложности при портировании или эмуляции кода других процессорных архитектур, например, i386 или MIPS. Предложение о внедрении BWX в базовый набор команд Alpha появилось в июне 1994 с подачи Ричарда Сайтса и было утверждено в июне 1995. Правда, для успешной работы BWX требовалась поддержка как со стороны процессора, так и со стороны чипсета. EV56 производился с тактовыми частотами от 366МГц до 666МГц (TDP от 31Вт до 55Вт), начиная с лета 1996. Samsung также выпускал EV56, по лицензионному соглашению с DEC от июня 1996 (версию на 666МГц производил только он). Содержал 9,66 млн. транзисторов, площадь ядра составляла 209 кв.мм., использовалось двойное напряжение (2,5В на основную логику и 3,3В на входные-выходные цепи).     17 марта 1997 был представлен 21164PC (PCA56), бюджетный вариант EV56, спроектированный совместно DEC и Mitsubishi. Отсутствовал S-cache и соответствующая логика, зато размер I-cache был увеличен вдвое (до 16Кб). Содержал 3,5 млн. транзисторов, имел площадь ядра в 141 кв.мм., использовал тот же техпроцесс и напряжение питания, что и EV56; форм-фактор процессора изменился: IPGA-413 против IPGA-499. Выпускался с тактовыми частотами от 400МГц до 533МГц (TDP от 26Вт до 35Вт). В будущем, на производственных мощностях Samsung, также выпускался 0,28µ вариант 21164PC (PCA57), с удвоенными размерами I-cache и D-cache, причём первый использовал 2-канальную ассоциативность. Количество транзисторов в ядре увеличилось до 5,7 млн., а его площадь уменьшилась (до 101 кв.мм.); был спроектирован под пониженное напряжение питания (2,0В на основную логику и 2,5В на входные-выходные цепи), с тактовыми частотами от 533МГц до 666МГц (TDP от 18Вт до 23Вт).   Кроме унаследованных от EV56 инструкций BWX, PCA56 поддерживал новый набор MVI (Motion Video Instructions), предназначенный для ускорения алгоритмов обработки видео и аудио потоков по принципу SIMD (Single Instruction -- Multiple Data), в некоторой мере сопоставимый с MMX. Кроме унаследованных от EV56 инструкций BWX, PCA56 поддерживал новый набор MVI (Motion Video Instructions), предназначенный для ускорения алгоритмов обработки видео и аудио потоков по принципу SIMD (Single Instruction -- Multiple Data), в некоторой мере сопоставимый с MMX.   Первым стандартным чипсетом, разработанным для EV5, был DEC Alcor (21171). Он поддерживал частоту системной шины в 33МГц, до 64Мб B-cache, до 8Гб памяти FPM ECC (используя шину памяти разрядностью в 256 бит), а также 64-битную шину PCI (33МГц). Поддержка шины ISA (EISA) могла быть реализована посредством стандартного моста, как и прежде. Встроенного контроллера IDE также не было (мог устанавливаться отдельной микросхемой других производителей). Физически чипсет состоял из 5 чипов: 1 универсального контроллера (включающего поддержку шины PCI), и 4 коммутаторов данных (data switch). Одновременно с запуском в производство EV56 была выпущена модификация Alcor, поддерживающая BWX -- Alcor 2 (21172). Дальнейшим развитием этой "чипсетной династии" стал одночиповый Pyxis (21174), который поддерживал системную шину с частотой в 66МГц и память SDRAM ECC 66МГц (правда, используя шину памяти с разрядностью в 128 бит). Для систем на основе PCA57 был разработан чипсет VLSI Polaris. Первым стандартным чипсетом, разработанным для EV5, был DEC Alcor (21171). Он поддерживал частоту системной шины в 33МГц, до 64Мб B-cache, до 8Гб памяти FPM ECC (используя шину памяти разрядностью в 256 бит), а также 64-битную шину PCI (33МГц). Поддержка шины ISA (EISA) могла быть реализована посредством стандартного моста, как и прежде. Встроенного контроллера IDE также не было (мог устанавливаться отдельной микросхемой других производителей). Физически чипсет состоял из 5 чипов: 1 универсального контроллера (включающего поддержку шины PCI), и 4 коммутаторов данных (data switch). Одновременно с запуском в производство EV56 была выпущена модификация Alcor, поддерживающая BWX -- Alcor 2 (21172). Дальнейшим развитием этой "чипсетной династии" стал одночиповый Pyxis (21174), который поддерживал системную шину с частотой в 66МГц и память SDRAM ECC 66МГц (правда, используя шину памяти с разрядностью в 128 бит). Для систем на основе PCA57 был разработан чипсет VLSI Polaris.-------------------- Живы будем - Не помрем !

|

Сообщений в этой теме

SuperMax Alpha: история в фактах и комментариях 18.10.2015, 11:37

SuperMax Alpha: история в фактах и комментариях 18.10.2015, 11:37

SuperMax [b]

Часть 1. PDP и VAX

[b]Digital Equipment Corp... 18.10.2015, 14:35

SuperMax [b]

Часть 1. PDP и VAX

[b]Digital Equipment Corp... 18.10.2015, 14:35

SuperMax [b]Часть 2. Проект PRISM

[img]http://www1.fcenter.... 18.10.2015, 14:35

SuperMax [b]Часть 2. Проект PRISM

[img]http://www1.fcenter.... 18.10.2015, 14:35

SuperMax [b]Часть 4. EV4, LCA4, EV45, LCA45

[img]http://www... 18.10.2015, 14:39

SuperMax [b]Часть 4. EV4, LCA4, EV45, LCA45

[img]http://www... 18.10.2015, 14:39

SuperMax [b]Часть 6. Крах DEC

[img]http://www1.fcenter.ru/i... 18.10.2015, 14:46

SuperMax [b]Часть 6. Крах DEC

[img]http://www1.fcenter.ru/i... 18.10.2015, 14:46

SuperMax [b]Часть 7. EV6, EV67, EV68C, EV68A

[img]http://ww... 18.10.2015, 14:55

SuperMax [b]Часть 7. EV6, EV67, EV68C, EV68A

[img]http://ww... 18.10.2015, 14:55

SuperMax [b]Часть 8. Эпоха Compaq

[img]http://www1.fcenter.... 18.10.2015, 14:57

SuperMax [b]Часть 8. Эпоха Compaq

[img]http://www1.fcenter.... 18.10.2015, 14:57

SuperMax Часть 9. EV7, EV79, EV7z, EV8

http://www1.fcenter.... 18.10.2015, 14:59

SuperMax Часть 9. EV7, EV79, EV7z, EV8

http://www1.fcenter.... 18.10.2015, 14:59

SuperMax [b]Литература

1. Rich Witek, Dick Sites. Alpha Ar... 18.10.2015, 15:02

SuperMax [b]Литература

1. Rich Witek, Dick Sites. Alpha Ar... 18.10.2015, 15:02  |

2 чел. читают эту тему (гостей: 2, скрытых пользователей: 0)

Пользователей: 0

| Текстовая версия | Сейчас: 13.5.2026, 12:18 |