Здравствуйте, гость ( Вход | Регистрация )

| SuperMax |

18.10.2015, 11:37 18.10.2015, 11:37

Сообщение

#1

|

Администратор      Группа: Root Admin Сообщений: 6 377 Регистрация: 7.1.2006 Из: Красноярск Пользователь №: 1 |

Dig my grave both long and narrow  Make my coffin neat and strong Make my coffin neat and strong (из старой американской песни) (из старой американской песни) Вступление  Данный труд открывает цикл статей, посвящённых процессорам и архитектуре Alpha, а также многому с ними связанному. Цикл, потому что изложение всего имеющегося материала в виде одного обзора показалось автору довольно проблематичным и неуместным. К тому же, открываемая тема является действительно многогранной и во многих аспектах фундаментальной, не имеющей прецедентов в плане полноты и масштабности изложения, поэтому вполне заслуживает пристального и подробного рассмотрения. Возможно, эта и последующие статьи смотрелись бы более уместно лет 5 назад, когда Alpha-процессоры ставили очередные рекорды производительности и масштабируемости, a их будущее ожидалось совсем не таким, каким оно выглядит с точки зрения дня сегодняшнего. Однако, именно в наше время можно уверенно подвести финальную черту под этой сагой, посвященной одной из самых интересных и перспективных компьютерных архитектур. Данный труд открывает цикл статей, посвящённых процессорам и архитектуре Alpha, а также многому с ними связанному. Цикл, потому что изложение всего имеющегося материала в виде одного обзора показалось автору довольно проблематичным и неуместным. К тому же, открываемая тема является действительно многогранной и во многих аспектах фундаментальной, не имеющей прецедентов в плане полноты и масштабности изложения, поэтому вполне заслуживает пристального и подробного рассмотрения. Возможно, эта и последующие статьи смотрелись бы более уместно лет 5 назад, когда Alpha-процессоры ставили очередные рекорды производительности и масштабируемости, a их будущее ожидалось совсем не таким, каким оно выглядит с точки зрения дня сегодняшнего. Однако, именно в наше время можно уверенно подвести финальную черту под этой сагой, посвященной одной из самых интересных и перспективных компьютерных архитектур.  Эта статья является, в значительной мере, историческим очерком с элементами анализа, поэтому её следует рассматривать именно в этом аспекте. В целом, она не претендует на универсальность, хотя и содержит значительное количество справочной информации. С другой стороны, рассматривать её как некролог или надгробную молитву также явно не стоит... Эта статья является, в значительной мере, историческим очерком с элементами анализа, поэтому её следует рассматривать именно в этом аспекте. В целом, она не претендует на универсальность, хотя и содержит значительное количество справочной информации. С другой стороны, рассматривать её как некролог или надгробную молитву также явно не стоит... -------------------- Живы будем - Не помрем !

|

|

Ответов

| SuperMax |

18.10.2015, 14:55 18.10.2015, 14:55

Сообщение

#2

|

Администратор      Группа: Root Admin Сообщений: 6 377 Регистрация: 7.1.2006 Из: Красноярск Пользователь №: 1 |

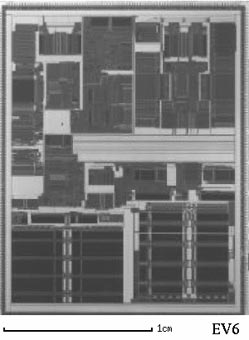

Часть 7. EV6, EV67, EV68C, EV68A  Хотя процессор 21264 (EV6) был разработан в DEC, и первая информация о нем была опубликована в октябре 1996 на Microprocessor Forum, окончательное воплощение в кремнии датируется февралём 1998, когда DEC уже была в процессе ликвидации. Собственно процессор представлял собой довольно существенный шаг вперед по сравнению с EV5, во многих аспектах революционный. Одним из основных нововведений было внеочередное исполнение (out-of-order execution) инструкций, повлёкшее за собой фундаментальную реорганизацию ядра, и снизившую зависимость основных фунциональных устройств от пропускной способности кэшей и оперативной памяти. EV6 мог переупорядочить на лету до 80 инструкций, а это значительно больше, чем у других конкурентных разработок (к слову, архитектура Intel P6 предусматривала внеочередную обработку до 40 [микрокоманд], HP PA-8x00 -- до 56, MIPS R12000 -- до 48, IBM Power3 -- до 32, а PowerPC G4 -- до 5; разработанный к тому времени Sun UltraSPARC II переупорядочивание команд не поддерживал). Внеочередное исполнение дополнялось техникой переименования регистров (register renaming), и для этого в ядро было встроено дополнительно 48 целочисленных и 40 вещественных физических регистров (количество логических, то есть программных, осталось неизменным). Хотя процессор 21264 (EV6) был разработан в DEC, и первая информация о нем была опубликована в октябре 1996 на Microprocessor Forum, окончательное воплощение в кремнии датируется февралём 1998, когда DEC уже была в процессе ликвидации. Собственно процессор представлял собой довольно существенный шаг вперед по сравнению с EV5, во многих аспектах революционный. Одним из основных нововведений было внеочередное исполнение (out-of-order execution) инструкций, повлёкшее за собой фундаментальную реорганизацию ядра, и снизившую зависимость основных фунциональных устройств от пропускной способности кэшей и оперативной памяти. EV6 мог переупорядочить на лету до 80 инструкций, а это значительно больше, чем у других конкурентных разработок (к слову, архитектура Intel P6 предусматривала внеочередную обработку до 40 [микрокоманд], HP PA-8x00 -- до 56, MIPS R12000 -- до 48, IBM Power3 -- до 32, а PowerPC G4 -- до 5; разработанный к тому времени Sun UltraSPARC II переупорядочивание команд не поддерживал). Внеочередное исполнение дополнялось техникой переименования регистров (register renaming), и для этого в ядро было встроено дополнительно 48 целочисленных и 40 вещественных физических регистров (количество логических, то есть программных, осталось неизменным).  Количество целочисленных конвейеров было увеличено до 4 (организованных в 2 кластера), но функционально они были несколько неоднородны: 2-й конвейер мог выполнять операции умножения (7 тактов на инструкцию) и сдвига (1 такт), а 4-й -- MVI (3 такта) и сдвига; кроме того, все 4 конвейера поддерживали отработку элементарных арифметических и логических операций (1 такт). Каждый кластер располагал своим файлом целочисленных регистров (как упомянуто выше, на 80 записей), содержимое которых было идентично (синхронизировалось). 1-й и 3-й конвейеры также выполняли некоторые функции A-box, рассчитывая виртуальные адреса для операций загрузки/сохранения. Собственно A-box работал с I-TLB и D-TLB (каждый на 128 записей), очередями загрузки и сохранения (каждая по 32 команды), и 8 64-байтными буферами (miss address file) для операций с B-cache и основной памятью. Вещественные конвейеры также были функционально различны: 1-й поддерживал операции сложения (4 такта), деления (12 тактов для одинарной точности и 15 тактов для двойной), вычисления квадратного корня (15 и 30 тактов), а 2-й -- только умножения (4 такта). Между прочим, блок вычисления квадратного корня и соответствующие инструкции были нововведениями для архитектуры Alpha. Декодер, как и прежде в EV5, подавал до 4 инструкций за такт, а планировщик распределял их в 2 очереди: на целочисленные конвейеры (I-queue, 20 команд), и на вещественные конвейеры (F-queue, 15 команд). Кроме вычисления квадратного корня, были добавлены инструкции предварительной выборки, а также команды для переноса данных между целочисленными и вещественными регистрами. Количество целочисленных конвейеров было увеличено до 4 (организованных в 2 кластера), но функционально они были несколько неоднородны: 2-й конвейер мог выполнять операции умножения (7 тактов на инструкцию) и сдвига (1 такт), а 4-й -- MVI (3 такта) и сдвига; кроме того, все 4 конвейера поддерживали отработку элементарных арифметических и логических операций (1 такт). Каждый кластер располагал своим файлом целочисленных регистров (как упомянуто выше, на 80 записей), содержимое которых было идентично (синхронизировалось). 1-й и 3-й конвейеры также выполняли некоторые функции A-box, рассчитывая виртуальные адреса для операций загрузки/сохранения. Собственно A-box работал с I-TLB и D-TLB (каждый на 128 записей), очередями загрузки и сохранения (каждая по 32 команды), и 8 64-байтными буферами (miss address file) для операций с B-cache и основной памятью. Вещественные конвейеры также были функционально различны: 1-й поддерживал операции сложения (4 такта), деления (12 тактов для одинарной точности и 15 тактов для двойной), вычисления квадратного корня (15 и 30 тактов), а 2-й -- только умножения (4 такта). Между прочим, блок вычисления квадратного корня и соответствующие инструкции были нововведениями для архитектуры Alpha. Декодер, как и прежде в EV5, подавал до 4 инструкций за такт, а планировщик распределял их в 2 очереди: на целочисленные конвейеры (I-queue, 20 команд), и на вещественные конвейеры (F-queue, 15 команд). Кроме вычисления квадратного корня, были добавлены инструкции предварительной выборки, а также команды для переноса данных между целочисленными и вещественными регистрами.  Структура C-box подверглась значительным изменениям: теперь он работал только с 2 уровнями кэш-памяти. Интегрированный в ядро L1 состоял из 64Кб I-cache и 64Кб D-cache, оба с 2-канальной ассоциативностью и 64-байтными строками, причем D-cache работал в режиме обратной записи, хотя всё так же дублировался в B-cache. Из-за значительных размеров и усложнённой организации задержки D-cache при чтении/записи были увеличены до 3 тактов (в/из целочисленного регистра) и 4 тактов (в/из вещественного регистра). D-cache так и остался двухпортовым, но, в отличие от EV5, он уже не состоял из 2 одинаковых частей, синхронизированных по записи, а был просто заведён на удвоенной частоте. Внешний B-cache, размером от 1Мб до 16Мб с прямым отображением и обратной записью, использовал независимую 128-битную двунаправленную шину данных (с дополнительными 16 битами для ECC), а также независимую 20-битную однонаправленную шину шину адреса; набирался на микросхемах LW SSRAM (late-write, с отложенной записью), а позднее и DDR SSRAM (double data rate, с удвоенной скоростью передачи данных); частота B-cache программировалась (от 2/3 до 1/8 частоты ядра), и, в отличие от предыдущих поколений процессоров Alpha, собственно B-cache не был опциональным. Системная шина данных была только 64-битной (с дополнительными 8 битами для ECC), двунаправленной, но использовала технологию DDR. Системная шина адреса была 44-битной, физически представленная в виде двух 15-битных однонаправленных каналов, без поддержки DDR. 15-битная системная шина управления DDR также не поддерживала. Был изменён базовый принцип работы системной шины, которая теперь стала выделенной (вместо разделяемой), то есть каждый процессор имел свой путь к чипсету. Структура C-box подверглась значительным изменениям: теперь он работал только с 2 уровнями кэш-памяти. Интегрированный в ядро L1 состоял из 64Кб I-cache и 64Кб D-cache, оба с 2-канальной ассоциативностью и 64-байтными строками, причем D-cache работал в режиме обратной записи, хотя всё так же дублировался в B-cache. Из-за значительных размеров и усложнённой организации задержки D-cache при чтении/записи были увеличены до 3 тактов (в/из целочисленного регистра) и 4 тактов (в/из вещественного регистра). D-cache так и остался двухпортовым, но, в отличие от EV5, он уже не состоял из 2 одинаковых частей, синхронизированных по записи, а был просто заведён на удвоенной частоте. Внешний B-cache, размером от 1Мб до 16Мб с прямым отображением и обратной записью, использовал независимую 128-битную двунаправленную шину данных (с дополнительными 16 битами для ECC), а также независимую 20-битную однонаправленную шину шину адреса; набирался на микросхемах LW SSRAM (late-write, с отложенной записью), а позднее и DDR SSRAM (double data rate, с удвоенной скоростью передачи данных); частота B-cache программировалась (от 2/3 до 1/8 частоты ядра), и, в отличие от предыдущих поколений процессоров Alpha, собственно B-cache не был опциональным. Системная шина данных была только 64-битной (с дополнительными 8 битами для ECC), двунаправленной, но использовала технологию DDR. Системная шина адреса была 44-битной, физически представленная в виде двух 15-битных однонаправленных каналов, без поддержки DDR. 15-битная системная шина управления DDR также не поддерживала. Был изменён базовый принцип работы системной шины, которая теперь стала выделенной (вместо разделяемой), то есть каждый процессор имел свой путь к чипсету.  Блок предсказания ветвлений был полностью переработан. Теперь он был организован по 2-уровневой схеме: с локальной историей переходов (local history table, 1024 записи с 10-битными счетчиками) и локальным предсказателем (local predictor, 1024 записи по 3 бита), а также с глобальным предсказателем (global predictor, 4096 записей по 3 бита) и 12-битным "путем истории" (history path). Оба алгоритма работали независимо, и если локальный отслеживал каждый отдельный условный переход, то глобальный -- последовательности переходов. Общий предсказатель ветвлений анализировал результаты обоих алгоритмов, и делал выводы в виде отдельной таблицы выборочного предсказателя (choice predictor, 4096 записей по 2 бита), на основе которой выводились предпочтения при расхождении локальных и глобальных прогнозов. Такой кооперативный метод позволял добиться лучших результатов, чем применение любого из подходов в отдельности. Блок предсказания ветвлений был полностью переработан. Теперь он был организован по 2-уровневой схеме: с локальной историей переходов (local history table, 1024 записи с 10-битными счетчиками) и локальным предсказателем (local predictor, 1024 записи по 3 бита), а также с глобальным предсказателем (global predictor, 4096 записей по 3 бита) и 12-битным "путем истории" (history path). Оба алгоритма работали независимо, и если локальный отслеживал каждый отдельный условный переход, то глобальный -- последовательности переходов. Общий предсказатель ветвлений анализировал результаты обоих алгоритмов, и делал выводы в виде отдельной таблицы выборочного предсказателя (choice predictor, 4096 записей по 2 бита), на основе которой выводились предпочтения при расхождении локальных и глобальных прогнозов. Такой кооперативный метод позволял добиться лучших результатов, чем применение любого из подходов в отдельности.  При разработке EV6, учитывая большое число и сложность организации взаимодействия функциональных устройств, была полностью переработана схема расположения генераторов тактовых частот. Более равномерное распространение тактового сигнала позволило ядру работать на частотах, равных частотам куда более простого ядра EV56, при использовании того же техпроцесса. В общем, потребляемая чатотными генераторами мощность составляла для EV6 около 32% от общего потребления ядра; для сравнения, у EV56 этот показатель был около 25%, у EV5 -- около 37%, у EV4 -- около 40%. При разработке EV6, учитывая большое число и сложность организации взаимодействия функциональных устройств, была полностью переработана схема расположения генераторов тактовых частот. Более равномерное распространение тактового сигнала позволило ядру работать на частотах, равных частотам куда более простого ядра EV56, при использовании того же техпроцесса. В общем, потребляемая чатотными генераторами мощность составляла для EV6 около 32% от общего потребления ядра; для сравнения, у EV56 этот показатель был около 25%, у EV5 -- около 37%, у EV4 -- около 40%. Физически EV6 производился по той же 6-слойной 0,35µ CMOS6 технологии, что и EV56, состоял из 15,2 млн. транзисторов (из них около 9 млн. на I-cache, D-cache, и предсказатели переходов), имел площадь ядра в 314 кв.мм., и был рассчитан на рабочее напряжение от 2,1В до 2,3В. Тактовые частоты составляли от 466МГц до 600МГц (TDP прибл. от 80Вт до 110Вт). Форм-фактор: PGA-587 (Pin Grid Array).     В конце 1999 на рынок вышел 21264А (EV67), выполненный по 0,25µ CMOS7 техпроцессу от Samsung, с площадью ядра в 210 кв.мм., и пониженным рабочим напряжением в 2,0В. Никаких архитектурных изменений по сравнению с EV6 не наблюдалось. Тактовые частоты составили от 600МГц до 833МГц (TDP прибл. от 70Вт до 100Вт), что позволило Alpha вернуть лидерство на целочисленных операциях, незадолго до этого утраченное в пользу процессоров Intel и AMD.   В начале 2000 появились первые процессоры 21264B (EV68C), на этот раз от IBM, по 0,18µ CMOS8 техпроцессу с использованием медных проводников. Несмотря на прежнее отсутствие архитектурных изменений, многообещающая технология позволила поднять тактовые частоты сразу до 1250МГц. В 2001 Samsung смог наладить производство 21264B (EV68А) по своему 0,18µ техпроцессу, но с алюминиевыми проводниками, сократив площадь ядра до 125 кв.мм., и уменьшив напряжение питания до 1,7В, что позволило вывести тактовые частоты в диапазон от 750МГц до 940МГц (TDP прибл. от 60Вт до 75Вт). В начале 2000 появились первые процессоры 21264B (EV68C), на этот раз от IBM, по 0,18µ CMOS8 техпроцессу с использованием медных проводников. Несмотря на прежнее отсутствие архитектурных изменений, многообещающая технология позволила поднять тактовые частоты сразу до 1250МГц. В 2001 Samsung смог наладить производство 21264B (EV68А) по своему 0,18µ техпроцессу, но с алюминиевыми проводниками, сократив площадь ядра до 125 кв.мм., и уменьшив напряжение питания до 1,7В, что позволило вывести тактовые частоты в диапазон от 750МГц до 940МГц (TDP прибл. от 60Вт до 75Вт).  В разных источниках проскакивали упоминания о 21264C и 21264D, с кодовыми именами EV68CB и EV68DC, выпускавшимися IBM по той же технологии, что и EV68C, и с теми же частотными характеристиками, поэтому их можно расматривать как частные варианты последнего. Единственным существенным отличием было использование нового форм-фактора, "безногого" CLGA-675 (Ceramic Land Grid Array) вместо PGA-587.   Для процессоров серии 21264 было спроектировано 2 чипсета: DEC Tsunami (21272; он же Typhoon) и AMD Irongate (AMD-751), хотя их могло бы быть значительно больше, ввиду того, что и 21264, и Athlon использовали почти одинаковую системную шину (она была лицензирована AMD ещё у DEC). Для процессоров серии 21264 было спроектировано 2 чипсета: DEC Tsunami (21272; он же Typhoon) и AMD Irongate (AMD-751), хотя их могло бы быть значительно больше, ввиду того, что и 21264, и Athlon использовали почти одинаковую системную шину (она была лицензирована AMD ещё у DEC).  DEC Tsunami был чипсетом повышенной масштабируемости. На его основе проектировали как однопроцессорные, так двухпроцессорные и четырехпроцессорные системы, с разрядностью шины памяти от 128 до 512 бит (SDRAM ECC registered, 83МГц), поддержкой как одной, так и нескольких шин PCI (64-бит, 33МГц). Такой гибкости удалось достичь благодаря разделению чипсета на отдельные компоненты: контроллеры системной шины (C-chips, по одному на каждый процессор), контроллеры шины памяти (D-chips, по одному на каждые 64 бита ширины шины), и контроллеры шины PCI (P-chips, по одному на каждую требуемую шину). Поэтому ничего удивительного, что в некоторых системах (например, AlphaPC 264DP) чипсеты состояли из 12 микросхем... DEC Tsunami был чипсетом повышенной масштабируемости. На его основе проектировали как однопроцессорные, так двухпроцессорные и четырехпроцессорные системы, с разрядностью шины памяти от 128 до 512 бит (SDRAM ECC registered, 83МГц), поддержкой как одной, так и нескольких шин PCI (64-бит, 33МГц). Такой гибкости удалось достичь благодаря разделению чипсета на отдельные компоненты: контроллеры системной шины (C-chips, по одному на каждый процессор), контроллеры шины памяти (D-chips, по одному на каждые 64 бита ширины шины), и контроллеры шины PCI (P-chips, по одному на каждую требуемую шину). Поэтому ничего удивительного, что в некоторых системах (например, AlphaPC 264DP) чипсеты состояли из 12 микросхем...  Хотя AMD Irongate разрабатывался изначально как северный мост для материнских плат, предназначенных для процессоров Athlon, его также использовали в некоторых материнских платах для Alpha (например, UP1000 и UP1100). Так как он был одночиповым решением, то стоил намного дешевле DEC Tsunami и отличался существенно более низким энергопотреблением. Однако, его возможности не соответствовали потенциалу 21264 из-за отсутствия поддержки многопроцессорности и слишком узкой шины памяти (64-бит, SDRAM ECC unbuffered, 100МГц). Тем не менее, Irongate был первым чипсетом для Alpha с поддержкой шины AGP. И последним. Хотя AMD Irongate разрабатывался изначально как северный мост для материнских плат, предназначенных для процессоров Athlon, его также использовали в некоторых материнских платах для Alpha (например, UP1000 и UP1100). Так как он был одночиповым решением, то стоил намного дешевле DEC Tsunami и отличался существенно более низким энергопотреблением. Однако, его возможности не соответствовали потенциалу 21264 из-за отсутствия поддержки многопроцессорности и слишком узкой шины памяти (64-бит, SDRAM ECC unbuffered, 100МГц). Тем не менее, Irongate был первым чипсетом для Alpha с поддержкой шины AGP. И последним.-------------------- Живы будем - Не помрем !

|

Сообщений в этой теме

SuperMax Alpha: история в фактах и комментариях 18.10.2015, 11:37

SuperMax Alpha: история в фактах и комментариях 18.10.2015, 11:37

SuperMax [b]

Часть 1. PDP и VAX

[b]Digital Equipment Corp... 18.10.2015, 14:35

SuperMax [b]

Часть 1. PDP и VAX

[b]Digital Equipment Corp... 18.10.2015, 14:35

SuperMax [b]Часть 2. Проект PRISM

[img]http://www1.fcenter.... 18.10.2015, 14:35

SuperMax [b]Часть 2. Проект PRISM

[img]http://www1.fcenter.... 18.10.2015, 14:35

SuperMax [b]Часть 4. EV4, LCA4, EV45, LCA45

[img]http://www... 18.10.2015, 14:39

SuperMax [b]Часть 4. EV4, LCA4, EV45, LCA45

[img]http://www... 18.10.2015, 14:39

SuperMax [b]Часть 5. EV5, EV56, PCA56, PCA57

[img]http://ww... 18.10.2015, 14:44

SuperMax [b]Часть 5. EV5, EV56, PCA56, PCA57

[img]http://ww... 18.10.2015, 14:44

SuperMax [b]Часть 6. Крах DEC

[img]http://www1.fcenter.ru/i... 18.10.2015, 14:46

SuperMax [b]Часть 6. Крах DEC

[img]http://www1.fcenter.ru/i... 18.10.2015, 14:46

SuperMax [b]Часть 8. Эпоха Compaq

[img]http://www1.fcenter.... 18.10.2015, 14:57

SuperMax [b]Часть 8. Эпоха Compaq

[img]http://www1.fcenter.... 18.10.2015, 14:57

SuperMax Часть 9. EV7, EV79, EV7z, EV8

http://www1.fcenter.... 18.10.2015, 14:59

SuperMax Часть 9. EV7, EV79, EV7z, EV8

http://www1.fcenter.... 18.10.2015, 14:59

SuperMax [b]Литература

1. Rich Witek, Dick Sites. Alpha Ar... 18.10.2015, 15:02

SuperMax [b]Литература

1. Rich Witek, Dick Sites. Alpha Ar... 18.10.2015, 15:02  |

2 чел. читают эту тему (гостей: 2, скрытых пользователей: 0)

Пользователей: 0

| Текстовая версия | Сейчас: 13.5.2026, 12:18 |